基于FPGA原型的GPS基帶驗證系統設計與實現

隨著SoC設計復雜度的提高,驗證所需時間已經占到整個設計周期的70%以上,如何減少驗證時間成為一個十分重要的問題。GPS基帶芯片是一個典型的SoC,其主要功能模塊是相關器,用以實現GPS信號的解調和解擴。相關器占據了基帶芯片中的大部分硬件資源,其仿真過程十分復雜且耗費大量時間,因此僅僅依靠軟件仿真是不現實的。隨著FPGA的性能和容量不斷提高,基于FPGA的原型驗證能夠減小開發風險,避免軟件仿真的缺點,加快產品上市時間,并且能夠真實地反映硬件的特性。這些優點使得基于FPGA的原型驗證越來越多地被用于SoC系統的設計過程。

1 從ASIC到FPGA原型的移植

理論上,FPGA原型驗證要與SoC的結構保持高度一致,但是,由于ASIC和FPGA結構上的差異,導致從ASIC到FPGA的移植需要做出適當的調整。

首先,當設計規模很大時,單片的FPGA容量不足以容納整個設計規模,需要2個或多個FPGA芯片來實現整個驗證系統。這時,FPGA之間的布線延時給整個系統的時序要求帶來困難,尤其對于高性能的設計。其次,結構上的差異導致的ASIC和FPGA IP模塊在時序上不兼容,需要額外的工作進行時序轉換。再次,某些硬IP核無法移植到FPGA上,需要構造適當的電路或者增加外圍輔助電路。

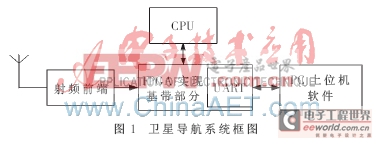

2 GPS基帶系統架構

整個GPS衛星導航系統包括前端射頻部分和基帶部分。前端射頻部分完成信號接收、濾波、AD轉換等;基帶部分完成GPS信號的解調、解擴、實現信號的跟蹤和捕獲。其系統框圖如圖1所示。

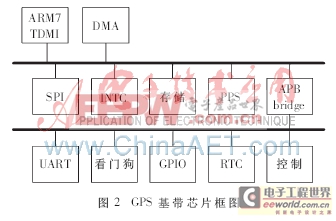

該衛星導航基帶芯片基于ARM7TDMI構建,擁有為捕獲跟蹤功能所設置的特殊硬件器件以及大量的常用外設。例如DMA、UART接口、SPI接口、GPIO、實時時鐘(RTC)等。256 KB的ROM和96 KB的SRAM用于存儲代碼和運行程序以及中間數據,并可外接FLASH進行程序調試及下載。其基帶框圖如圖2所示。

評論