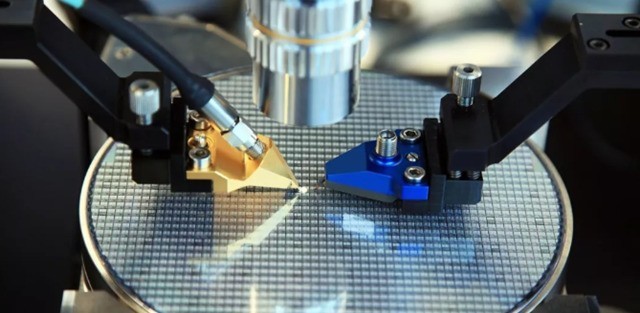

臺積電推出性能增強版的7nm和5nm制造工藝

近日外媒消息,臺積電已經(jīng)悄然推出了 7nm 深紫外(N7 / DUV)和 5nm 極紫外(N5 / EUV)制造工藝的性能增強版本。

本文引用地址:http://www.104case.com/article/201908/403303.htm其N7P 和 N5P 技術(shù),專為那些需要運行更快、消耗更少電量的客戶而設(shè)計。盡管 N7P 與 N7 的設(shè)計規(guī)則相同,但新工藝優(yōu)化了前端(FEOL)和中端(MOL)制程,可在同等功率下將性能提升 7%、或在同頻下降低 10% 的功耗。

在日本舉辦的 2019 VLSI 研討會上,臺積電透露了哪些客戶已經(jīng)可以用上新工藝,但該公司似乎并沒有廣而告之的想法。

N7P 采用經(jīng)過驗證的深紫外(DUV)光刻技術(shù),與 N7 相比,它沒有增加晶體管的密度。

有些需要高出約 18~20% 晶體管密度的 TSMC 客戶,預(yù)計需要使用臺積電的 N7+ 和 N6 工藝,后者使用極紫外(EUV)光刻技術(shù)進(jìn)行多層處理。

盡管 N7 和 N6 都是未來幾年的“長”節(jié)點,但臺積電會在下一個 N5 節(jié)點帶來顯著的密度、功耗和性能改進(jìn)。

N5 之后也會迎來一個叫做 N5P 的增強版本,輔以 FEOL 和 MOL 優(yōu)化,以便讓芯片在相同功率下提升 7% 的性能、或在同頻下降低 15% 的功耗。

(文中圖片來自互聯(lián)網(wǎng))

評論