5nm 文章 最新資訊

臺積電公布N2 2nm缺陷率:比3/5/7nm都要好

- 4月26日消息,在近日舉辦的北美技術論壇上,臺積電首次公開了N2 2nm工藝的缺陷率(D0)情況,比此前的7nm、5nm、3nm等歷代工藝都好的多。臺積電沒有給出具體數(shù)據(jù),只是比較了幾個工藝缺陷率隨時間變化的趨勢。臺積電N2首次引入了GAAFET全環(huán)繞晶體管,目前距離大規(guī)模量產還有2個季度,也就是要等到年底。N2試產近2個月來,缺陷率和同期的N5/N4差不多,還稍微低一點,同時顯著優(yōu)于N7/N6、N3/N3P。從試產到量產半年的時間周期內,N7/N6的綜合缺陷率是最高的,N3/N3P從量產開始就低得多了,

- 關鍵字: 臺積電 N2 2nm 缺陷率 3nm 5nm 7nm

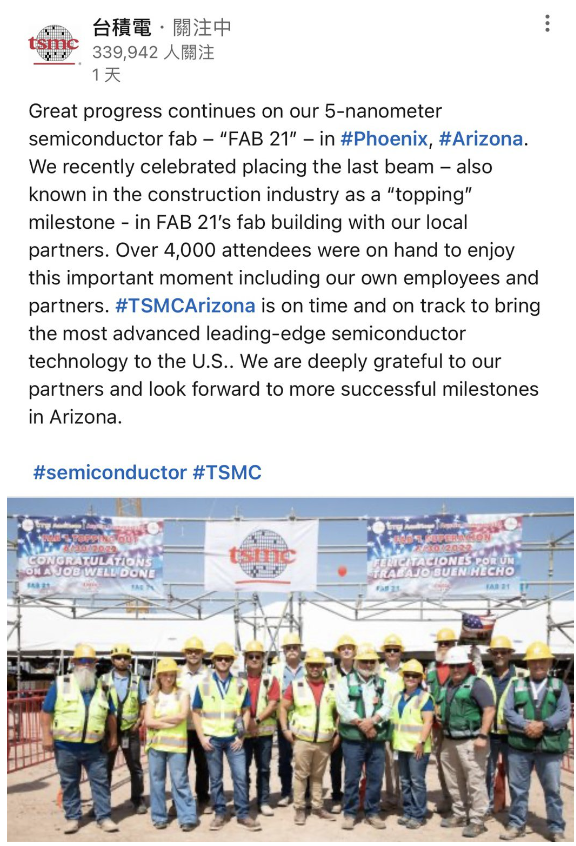

臺積電準備推出基于12和5nm工藝節(jié)點的下一代HBM4基礎芯片

- 在 HBM4 內存帶來的幾大變化中,最直接的變化之一就是內存接口的寬度。隨著第四代內存標準從已經(jīng)很寬的 1024 位接口升級到超寬的 2048 位接口,HBM4 內存堆棧將不會像以前一樣正常工作;芯片制造商需要采用比現(xiàn)在更先進的封裝方法,以適應更寬的內存。作為 2024 年歐洲技術研討會演講的一部分,臺積電提供了一些有關其將為 HBM4 制造的基礎模具的新細節(jié),這些模具將使用邏輯工藝制造。由于臺積電計劃采用其 N12 和 N5 工藝的變體來完成這項任務,該公司有望在 HBM4 制造工藝中占據(jù)有

- 關鍵字: 臺積電 12nm 5nm 工藝 HBM4 基礎芯片

Meta 展示新款 MTIA 芯片:5nm 工藝、90W 功耗、1.35GHz

- 4 月 11 日消息,Meta 公司于 2023 年 5 月推出定制芯片 MTIA v1 芯片之后,近日發(fā)布新聞稿,介紹了新款 MTIA 芯片的細節(jié)。MTIA v1 芯片采用 7nm 工藝,而新款 MTIA 芯片采用 5nm 工藝,采用更大的物理設計(擁有更多的處理核心),功耗也從 25W 提升到了 90W,時鐘頻率也從 800MHz 提高到了 1.35GHz。Meta 公司表示目前已經(jīng)在 16 個數(shù)據(jù)中心使用新款 MTIA 芯片,與 MTIA v1 相比,整體性能提高了 3 倍。但 Meta 只主動表示

- 關鍵字: Meta MTIA 芯片 5nm 工藝 90W 功耗 1.35GHz

使用半大馬士革工藝流程研究后段器件集成的工藝

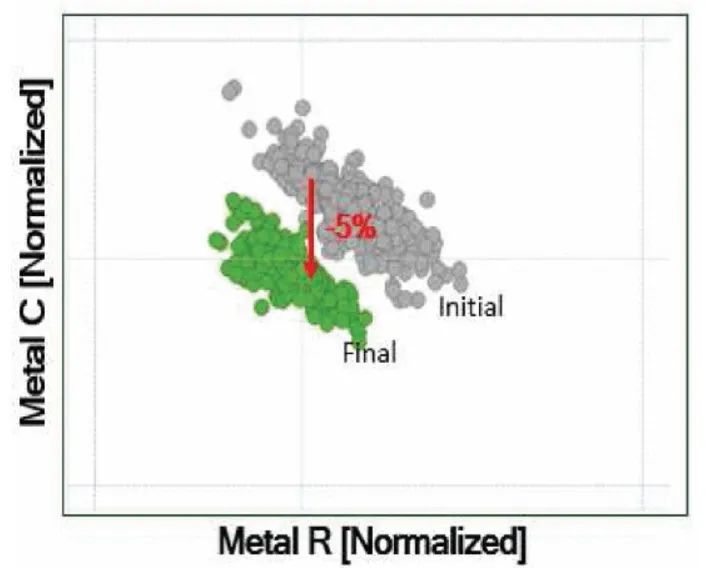

- ●? ?介紹隨著技術推進到1.5nm及更先進節(jié)點,后段器件集成將會遇到新的難題,比如需要降低金屬間距和支持新的工藝流程。為了強化電阻電容性能、減小邊緣定位誤差,并實現(xiàn)具有挑戰(zhàn)性的制造工藝,需要進行工藝調整。為應對這些挑戰(zhàn),我們嘗試在1.5nm節(jié)點后段自對準圖形化中使用半大馬士革方法。我們在imec生產了一組新的后段器件集成掩膜版,以對單大馬士革和雙大馬士革進行電性評估。新掩膜版的金屬間距分別為14nm、16nm、18nm、20nm和22nm,前兩類是1.5nm節(jié)點后段的最小目標金屬間距

- 關鍵字: 半大馬士革 后段器件集成 1.5nm SEMulator3D

4~5nm良率逐漸穩(wěn)定,客戶訂單增加?三星回應

- 據(jù)《科創(chuàng)板日報》報道,針對“因4~5納米先進制程良率逐漸穩(wěn)定,客戶訂單正逐漸增加,稼動率也相應反彈,12英寸稼動率回升至九成。”這一市場消息,三星半導體對其進行了回應。報道指出,三星半導體相關負責人回應表示,“暫無法透露最新良率或者客戶情況。正如我們在2022年4月的財務電話會議上所提及,5nm制程良率自去年年初以來已穩(wěn)定下來,而4nm制程良率也已得到了提升,自2022年第一季度以來一直在預期的軌道上。自此4~5nm制程良率已經(jīng)穩(wěn)定了。”據(jù)韓國媒體BusinessKorea報道,三星4納米制程良率相較之前

- 關鍵字: 5nm 良率 晶圓代工 三星

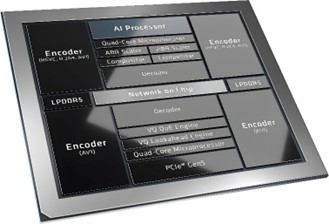

AMD 推出首款 5nm 基于 ASIC 的媒體加速器卡,開啟大規(guī)模交互式流媒體服務新時代

- 2023 年 4 月 6 日,加利福尼亞州圣克拉拉 — AMD (超威,納斯達克股票代碼:AMD)今日宣布推出 AMD Alveo? MA35D 媒體加速器,該卡具備兩個 5 納米基于 ASIC 的、支持 AV1 壓縮標準的視頻處理單元( VPU ),專為推動大規(guī)模直播互動流媒體服務新時代而打造。隨著全球視頻市場超 70% 的份額由直播內容主導1,一類新型的低時延、大容量交互式流媒體應用正在涌現(xiàn),例如連線觀賞、直播購物、在線拍賣和社交流媒體。?AMD Alveo MA35D 媒體加速器Alveo

- 關鍵字: AMD 5nm ASIC 媒體加速器卡 大規(guī)模交互式流媒體服務

第三大CPU架構RISC-V沖向5nm 192核 國產版也要來了:單核性能有驚喜

- 作為僅次于x86、ARM的第三大CPU架構,RISC-V憑借開源、免費的優(yōu)勢迅速發(fā)展,之前主要用于低功耗市場,但是現(xiàn)在也開始沖擊高性能領域,Ventana公司日前已經(jīng)做出了5nm 192核的芯片。Ventana公司日前發(fā)布了第一款產品Veyron V1,該公司研發(fā)了一種高性能RISC-V架構,每個CPU模塊中有16個RISC-V內核,頻率3.6GHz,整合48MB緩存,整個處理器可以集成12個CPU模塊,做到192核,臺積電5nm工藝生產制造,還有自己開發(fā)的高性能IO核心,延遲低至7ns,接近原生核心性能

- 關鍵字: RISC-V 5nm 192核

持續(xù)突破,概倫電子NanoSpice?通過三星代工廠5nm工藝技術認證

- 概倫電子宣布其高性能并行SPICE仿真器NanoSpice?通過三星代工廠5nm工藝技術認證,滿足雙方共同客戶對高精度、大容量和高性能的高端電路仿真需求。三星5nm工藝可以提高良率、降低功耗并改善性能,這就需要更高精度的電路仿真和驗證工具來實現(xiàn)更優(yōu)化的先進IC設計。NanoSpice?的認證屬于三星代工廠的EDA認證項目,該仿真器可支持最新版的OMI接口(開放模型接口),在模擬IP的大規(guī)模后仿網(wǎng)表仿真中表現(xiàn)出良好的仿真收斂性和準確性,幫助雙方共同客戶充滿信心地設計,縮短設計周期的同時確保更高精度。作為新一

- 關鍵字: 概倫電子 NanoSpice? 5nm

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司