國產3nm半導體來了?只是學術進展

今天,國內科研人員實現3nm晶體管技術具有重要意義,南華早報在文章中也提到了該技術的意義——過去我們只能看著別人競賽,現在可以參與這場競賽了。

本文引用地址:http://www.104case.com/article/201905/401058.htm不過這個技術具體如何呢?找了下,南華早報的新聞源是中科院微電子所的通告,官方介紹的內容如下:

現有硅基晶體管受玻爾茲曼熱力學限制,室溫下亞閾值擺幅SS≥60mV/dec,阻礙了工作電壓的繼續降低。當集成電路技術進入5納米及以下節點,隨著集成度的持續增加,在維持器件性能的同時面臨功耗急劇增加的嚴重挑戰。

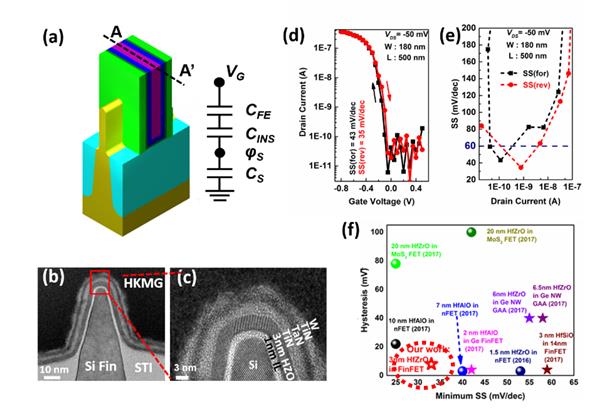

先導中心殷華湘研究員的團隊在主流后HKMG FinFET集成工藝的基礎上,通過材料工藝優化和多柵器件電容匹配設計,結合高質量低界面態的3納米鉿鋯金屬氧化物薄膜,研制成功性能優異的NC-FinFET器件,實現了SS和閾值電壓回滯分別為34.5mV/dec和9mV的500納米柵長NC-FinFET器件,以及SS和閾值電壓回滯分別為53mV/dec和40mV的20納米柵長NC-FinFET器件。

其中,500納米柵長NC-FinFET器件的驅動電流比常規HfO2基FinFET器件(非NC-FinFET)提升了260%且電流開關比(Ion/Ioff)大于1x106,標志著微電子所在新型NC-FinFET器件的研制方面取得了重要進展。

上述最新研究結果發表在國際微電子器件領域的頂級期刊《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2019.2891364),并迅速受到國際多家研發機構的高度關注。

該項集成電路先導工藝的創新研究得到國家科技重大專項02專項和國家重點研發計劃等項目的資助。

圖1 (a)負電容FinFET基本結構;(b-c)三維器件溝道結構與鐵電HZO膜層結構;

(d-e)器件I-V與SS特性;(f)最新器件性能國際綜合對比(SS與回滯電壓越小越好)

官方通報里用詞要嚴謹的多,提到的3nm實際上說的是3nm氧化物薄膜的厚度,沒有確定說是3nm工藝,不過這個技術也確實是用于5nm節點之后的工藝中。

不過這個所謂的負電容技術還是學術研究,南華報道中提到了殷華湘表示該技術具備應用實力,但是殷華湘也提到了這個技術距離商業化應用還有數年時間,團隊還在致力于解決材料及質量控制等問題。

簡單來說,這次的國產突破3nm工藝報道依然是一項重要的學術進展,但在半導體工藝上這樣的例子太多了,除非能很快量產并且具備更好的性能或者更低的成本,否則這些工藝很難取代現在的半導體技術。

評論