ISSCC 2019論文之引人矚目的高速接口

3-4)56Gb/s DSP Based TRX from eSilicon and MediaTek

本文引用地址:http://www.104case.com/article/201902/397947.htm這兩篇論文較為類似,都是采用7nm的DSP Based 56Gb/s Transceiver。他們的結構也是很常用的結構,從論文上來看沒有太多可說的。假如現在讓我來做一個新的56G系統規劃,我也會選這兩種結構中的一種。但他們的功耗都做得極為出色,eSilicon的單通道功耗才243mW,MediaTek的只給出了模擬部分的功耗,才180mW,充分展示了這兩個公司的設計優化能力。

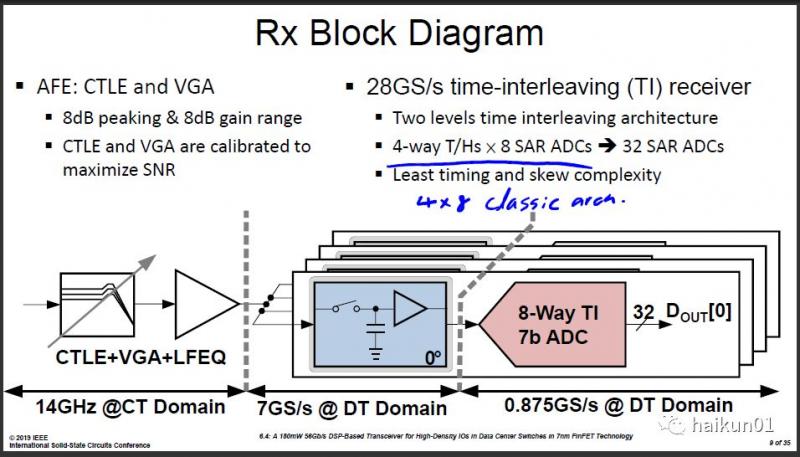

有一點有趣的地方是:MediaTek在RX端使用了4x8(4個Track/Hold,每個驅動8個SAR ADC Slice)的結構,這種是最常見的選擇。而eSilicon選擇了8x5(8個Track/Hold,每個驅動5個SAR ADC Slice),這樣他需要8個相位的8UI時鐘,在時鐘校準稍微復雜一點,一共8個Track/Hold,對前面CTLE引入的負載電容可能稍大,但每個Track/Hold的尺寸可以較小,每個Track/Hold有較長的時間來充放電。

最終哪一種結構較好?我可能傾向于4x8。但類似這種問題,似乎很難得到直接的證明。架構的比較取決于太多因素了。我們很少有機會把兩種架構都做成芯片,去測他們的性能直接對比。即使一種架構的測試結果稍好,那也有可能是這一組人的優化能力較強,不能直接證明架構的優勢。最終只能從架構的演化趨勢看出一點端倪。

5)100Gb/s PAM4 TRX from Inphi

又是一篇超過單通道100Gb/s的TRX,而且采用了DSP Based。

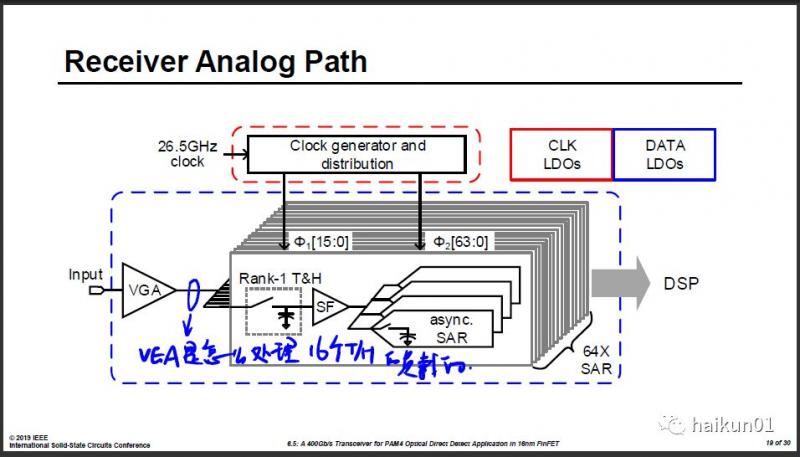

DSP based的100Gb/s的RX難點之一是ADC怎么選。56Gb/s常用的是4x8的結構,這樣一個Slice的速度差不多875MHz。到了112G,Slice本身的速度很難翻一倍,那只能采用空間換時間的策略,用更多路的time interleaved ADC來達到整體更高的速度。那么總共需要64個slice,這64個slice怎么分配呢,8x8還是16x4?這么大的寄生電容怎么來驅動?是一個超大的Buffer一起驅動這8個Track/Hold,還是分兩級?去年xilinx的112G RX論文就是一個大buffer驅動4個第二級buffer,然后每一個在驅動兩個Track/Hold。最終哪一種結構會勝出成為主流,現在還很難講。因為現在能做出112G的還太少了。

這篇inphi的論文在RX端選擇了16x4的結構,這樣VGA需要推動16個Track/Hold,而且從他的圖中VGA還沒有用電感拓展帶寬,我不知道他是怎么神奇的做出這么寬帶寬的。

評論