繼續縮小or改變封裝 誰是芯片未來的“康莊大道”?

隨著在單個die上集成各式各樣的功能模塊(部件)的成本持續上升,先進封裝正迅速成為芯片制造商的主流選擇。

盡管圍繞這一轉變已經有好幾年的討論,但實際情況是,它經歷了半個多世紀才得以實現。上世紀60年代,先進封裝始于IBM的倒裝芯片,而在20世紀90年代,隨著多芯片模組的出現,先進封裝技術又得到了進一步提升,特別是在mil/aero市場。盡管如此,先進封裝此前從未成為商業芯片制造商的首選,因為在硅領域,縮小特征尺寸的成本更低,針對等比例縮小的工具和IP生態系統已經很好地建立起來,并且從設計到盈利的時間(time-to-profitability)也更明確。

隨著finFETs和double patterning的引入,16/14nm節點處的經濟發生顯著變化。在更新的節點上,設計和制造成本將不斷增加。特征尺寸的縮小在5nm節點的過孔甚至和互連將需要新材料,5nm或3nm節點上需要新型晶體管結構(目前來看,最可能的是全柵FET)。此外需要高數值孔徑的EUV,以及新的刻蝕、沉積和檢測設備。總而言之,這些步驟增加了在先進工藝流程中開發和制造芯片的成本,能夠用足夠的體量來對沖這劇增成本的市場機會變得越來越少。

盡管EUV技術的持續延遲迫使設計團隊采用metal1和metal2的多重曝光,但上述的那些因素對于半導體行業來說并不意外。然而,行業需要時間來開發可行的替代方案,并證明和改進方案。EDA供應商正在提供設計工具和完整的流程,支持選擇各種封裝技術構建芯片,并且在高可見性市場(高知名度市場)中生產足夠的先進封裝芯片,以證明該方案是可行的,比如蘋果、AMD、華為、思科、IBM和賽靈思(Xilinx)等供應商,以及3D NAND、高帶寬內存(HBM)和混合內存立方體(Hybrid Memory Cube)等技術。

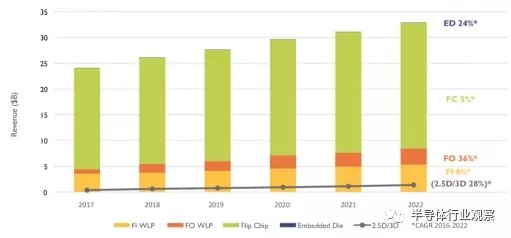

另外,在全球最大的IDM公司中,英特爾和三星現已提供低成本的專有橋接技術及代工服務。除了2.5D和3D封裝技術之外,所有主要的OSAT都提供一個或多個版本的扇出型晶圓級封裝(fan-out wafer-level packaging,fan-out WLP)技術。先進封裝各個領域的增長反映了這一現狀。

圖 1:不同平臺的先進封裝營收(縱坐標單位為十億美元)。資料來源:Yole Developpement研究機構于2017年5月發布的2017年先進封裝行業報告

自動化工具的設計

先進封裝市場增長的跡象之一是設計自動化工具的發展。在三大EDA供應商中,Cadence是率先提供封裝工具和解決方案。早在上個世紀九十年代,Cadence就進入了這一市場,自2000年以來,它一直基于模擬芯片設計并不能簡單套用等比例縮小原理的事實而從事相關的工具開發。而這一遠見花了近15年的時間,終于成為市場主流,其他EDA供應商也發現了封裝領域是一個值得投入研發的機會。

本月初,被西門子收購的Mentor推出了用于先進封裝的流程和新工具。該公司的高級IC封裝解決方案部門——Board Systems Division的產品營銷經理Keith Felton說:“這個工藝現在類似于硅工藝。我們預計將推出多個設計套件。因此,您將看到兩個用于fan-out晶圓級封裝的套件,每個封裝都有細微變化,同時還將推出堆疊die,基板上晶圓上芯片(chip on wafer on substrate,CoWoS),高引腳數倒裝芯片和系統級芯片封裝(system-in-package,SiP)等多種封裝技術”。

Felton表示,上述設計套件將與其他工具一起使用,包括DFMtools和PCB分析和驗證工具。

ANSYS總經理兼副總裁John Lee表示:“這些都是基于物理的仿真。這不僅僅是關于半導體的問題,還是熱分析和機械模擬。以臺積電的InFO技術硅片的晶圓級封裝為例,由于明顯的物理效應,需要進行同步熱學分析。這可能發生在7nm、10nm、16nm甚至更早的工藝節點。但散發熱量的元件將影響系統的可靠性。所以如果你考慮的是電遷移而不是熱效應,那你的分析可能會偏悲觀;然而如果所以,如果你談論的是電遷移而不是熱量,那么你可能對世界有一個悲觀的看法。如果你的觀點不是悲觀的,那將會很危險的”。

Synopsys公司董事長兼聯合首席執行官Aart de Geus表示,真正的關鍵在于將整個系統可視化,并構建跨封裝方案的組件和工具。“因此,在IP解決方案上,你必須對其進行描述使之在任何情況下都有效。整體仿真是對由各種形式的多個芯片組成的系統進行仿真,當然也包括軟件仿真。對設計人員來說,建立模型和原型的能力至關重要。包括針對數字和混合信號相關的設計”。

de Geus指出,它(代指上面的系統可視化?跨封裝方案的組件和工具?整體仿真?還是建立模型?我沒找到相關資料,前后文又聯系不起來,沒法準確翻譯)該解決方案還包括硬件模擬(emulation)和軟件原型,“不管是在封裝內部還是在7nm SoC上,你需要能夠在這些虛擬的硬件上運行軟件”。

但這些應用于先進封裝的工具,在預測的準確性上都還有很長一段路需要繼續探索。

“EDA設計工具將給半導體行業帶來巨大影響,”TechSearch International總裁Jan Vardaman表示:“如果沒有設計工具,很多事情都無法完成,未來工具應用將更加廣泛。在一個設計中,只要劃分允許,你想盡可能多地使用成熟工藝,為此,我們迫切需要設計工具。”

評論