高速數字電路封裝電源完整性分析

從圖4的測量結果,我們可以考到三種結構的GBN行為有很大的差異。首先考慮只有單一Pkg時的S參數,在1.3Ghz之前的行為像一個電容,在1.5Ghz后才有共振模態產生;考慮單一PCB,在0.5Ghz后就有共振模態產生,像0.73Ghz(TM01)、0.92Ghz(TM10)、1.17Ghz(TM11),其GBN行為比單一Pkg更糟。最后,考慮Pkg結合PCB,可以看到在1.5Ghz之前,比單一Pkg多了三個共振點,這些噪聲共振來自于PCB,通過錫球、Via等耦合到Pkg的電源上,這會使Pkg里的IC受噪聲影響更嚴重,這跟只考慮單一Pkg或PCB時有很大不同。

本文引用地址:http://www.104case.com/article/201610/311828.htm三、去耦電容對電源噪聲的影響

對于電源平面噪聲傳統的抑制方法是使用那個耦合電容,對于去耦電容的使用已有很多研究,但電容大小、位置、以及個數基本還是基于經驗法則。

去耦電容的理想位置

為了研究去耦電容位置PDS的影響,我們用上述Pkg+PCB結構,分別在Pkg和PCB上加去耦電容或兩者都加上去耦電容,通過量測|S21|來研究去耦電容的理想擺放位置。

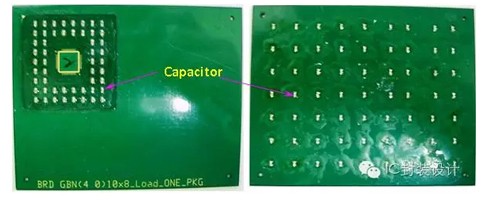

圖5 去耦電容安裝在Pkg和PCB上

如圖5所示,我們擺放電容的位置分三種情況,一是在Pkg上加52顆,二是在PCB上加63顆,三是在Pkg和PCB上同時各放置52和63顆,電容值大小為100nF, ESR、ESL分別為0.04ohm、0.63nH。量測結果如圖6。

圖6 加去耦電容于不同位置的|S21|比較圖

首先,把低頻到5Ghz分成三個階段,首先,開始低頻到500Mhz左右,不管在Pkg或PCB上加去耦電容,相比沒有加電容,都可以大大降低結構阻抗,減少GBN干擾。第二,對于0.5Ghz~2Ghz,在Pkg上和同時在Pkg與PCB上加去耦電容,對噪聲抑制效果差不多。可是如果只在PCB上加電容,可以看到在800Mhz附近多了一個共振點,這比沒有加電容時更糟。所以我們只在PCB上加電容時要特別注意,可能加上電容后電源噪聲更嚴重。第三,從2Ghz~5Ghz,三種加電容方式與沒加電容相比,效果并不明顯,因為此階段超過了電容本身的共振頻率,由于電容ESL的影響,隨著頻率升高,耦合電容逐漸失去作用,對較高頻的噪聲失去抑制效果。

去耦電容ESR的影響

在Pkg結合PCB結構上,放置12顆去耦電容,同時改變去耦電容的ESR,模擬結果如圖7所示。可以發現,當ESR值越來越大,會將極點鏟平,同時零點也被填平,使S21成為較為平坦的曲線。

圖7 去耦電容的ESR對|S21|的影響

去耦電容ESL的影響

在Pkg結合PCB結構上,放置12顆去耦電容,同時改變去耦電容的ESL,模擬結果如圖8所示。從圖中我們發現,ESL越大,共振點振幅越大,且有往低頻移動的趨勢,對噪聲的抑制能力越低。

圖8 去耦電容的ESL對|S21|的影響

評論