臺積電考慮在美國規劃CoWoS封裝廠:實現芯片“一條龍”本地化

近日在臺積電赴美召開董事會的行程期間,臺積電董事長兼總裁魏哲家在美國亞利桑那州舉行內部會議,作出了多項決議,加速先進制程赴美。

本文引用地址:http://www.104case.com/article/202502/467035.htm其中在先進制程部分,臺積電計劃在亞利桑那菲尼克斯建設的第三晶圓廠Fab 21 p將于今年年中動工,該晶圓廠將包含2nm和A16節點制程工藝,可能提早在2027年初試產、2028年量產,比原計劃提前至少一年到一年半。從臺積電供應鏈獲悉,未來將供應3nm產能的第二晶圓廠已完成主體廠房建設,正進行內部無塵室和機電整合工程,預計2026年一季度末開始工藝設備安裝,有望2026年底試產,2027下半年量產,進度快于此前公布的2028年投產。

對于半導體產業來說,制程只是其中一環,更為關鍵的還有先進封裝部分。臺積電考慮在美國規劃CoWoS封裝廠,以第一方的形式在美國供應AI GPU迫切需求的先進封裝產能,實現從芯片制造到成品封裝的在美“一條龍”本地化。值得注意的是,臺積電合作伙伴安靠(Amkor)已宣布建設和TSMC Arizona配套的先進封測產能;此外,臺積電競爭對手三星電子在《CHIPS》法案正式補貼協議中去掉了有關先進封裝的內容。

臺積電選擇在美國建設CoWoS封裝廠,不僅有利于自身業務的拓展,也有利于美國本土企業的需求。而更為重要的是,這種本地化的封裝生產模式,將有助于提高美國半導體產業的自主性和競爭力。

什么是CoWoS封裝技術

CoWoS技術的發展可以追溯到大約15年前,具體來說,是從臺積電開始考慮如何克服摩爾定律即將面臨的物理限制時開始的。起初,由于成本較高,CoWoS技術并未得到廣泛采用,只有賽靈思少量訂購;隨后經過一年的努力,推出改良版的先進封裝技術,這也成為臺積電日后可以打敗三星、英特爾的關鍵因素,隨著高性能計算(HPC)和人工智能(AI)領域的需求增長,CoWoS技術因其高集成度和優異性能而受到越來越多的關注。

CoWoS封裝技術是一種先進的芯片級封裝技術,能夠實現芯片之間的互聯互通,提高芯片的性能和可靠性。通過利用硅通孔(TSV)和微凸塊,與傳統的二維封裝方法相比,CoWoS可縮短互連長度、降低功耗并增強信號完整性。

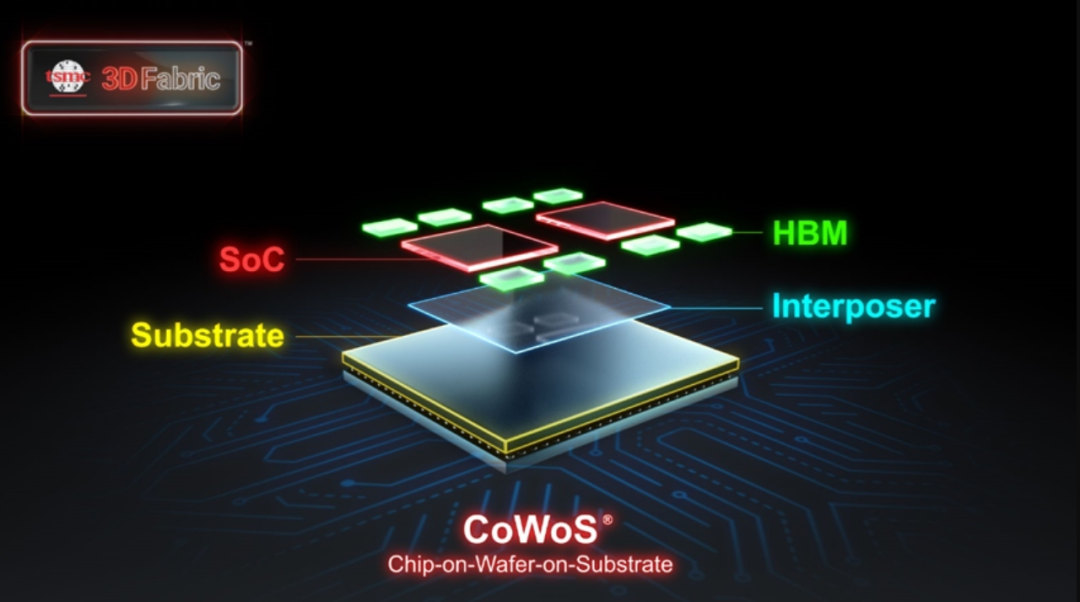

CoWos的全稱是Chip on Wafer on Substrate,通過在一個中介層(Interposer)上集成多個芯片(處理器和存儲器):就是先將芯片通過Chip on Wafer(CoW)的封裝制程連接至硅晶圓,再把CoW芯片與基板連接整合成CoWoS,達到減小封裝體積小的效果。

以前的系統面臨內存限制,而當代數據中心則采用高帶寬內存(HBM)來提高內存容量和帶寬,CoWoS技術可在同一集成電路平臺上實現邏輯SoC和HBM的異質集成。這種集成對于AI應用尤為重要,因為在AI應用中,大規模計算能力和快速數據訪問是最重要的。CoWoS將處理元件和內存元件就近配置,最大限度地減少了延遲,提高了吞吐量,從而為內存密集型任務帶來前所未有的性能提升。

CoWoS封裝流程可大致劃分為三個階段:

· 將裸片(Die)與中介層借由微凸塊(uBump)進行連接,并通過底部填充(Underfill)保護芯片與中介層的連接處;

· 將裸片與載板(Carrier)相連接,封裝基板(載板)是一類用于承載芯片的線路板,也是核心的半導體封測材料,具有高密度、高精度、高性能、小型化及輕薄化的特點,可為芯片提供支撐、散熱和保護的作用,同時也可為芯片與PCB母板之間提供電氣連接及物理支撐。在裸片與載板相連接后,利用化學拋光技術(CMP)將中介層進行薄化,此步驟目的在于移除中介層凹陷部分;

· 切割晶圓形成芯片,并將芯片連接至封裝基板;最后加上保護封裝的環形框和蓋板,使用熱介面金屬(TIM)填補與蓋板接合時所產生的空隙。

簡單來說就是我們可以把CoWos理解成一種拉近晶片與晶片之間距離進而促進運算效率的技術 —— 如果把晶片(處理器和存儲器)想象成是一排排大樓,那CoWos就是可以把每棟大樓都蓋的很近,甚至還有天橋和地下通道連接。這也就可以加速晶片之間的互聯效率,而沒有CoWos之前,每棟大樓獨立存在,互聯效率非常低。

最新版本CoWoS-L

目前使用的CoWoS技術可細分為S、R、L三類條線,分別為硅中介層(Si Interposer)、重布線層(RDL)與局部硅互聯技術(LSI)。

CoWoS-S

這種晶圓級系統集成平臺可提供多種插層尺寸、HBM立方體數量和封裝尺寸,可以實現大于2倍封裝尺寸(或約1700平方毫米)的中介層,并集成先進SoC芯片和四個以上HBM2/HBM2E存儲器。

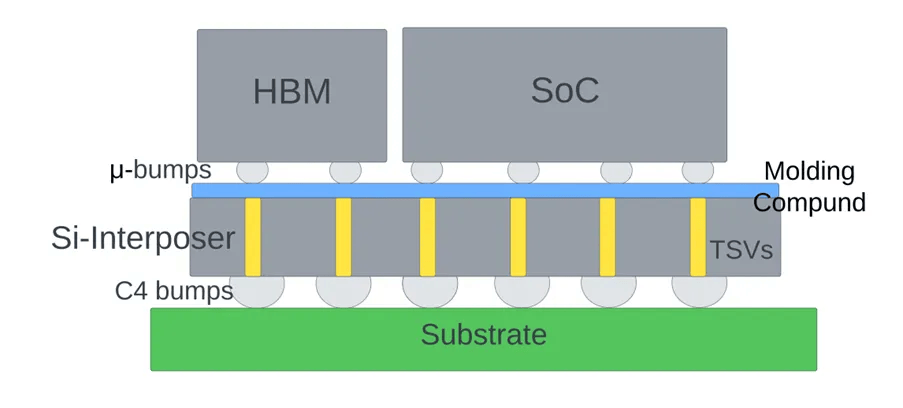

圖1:CoWoS-S封裝

該技術使用單片硅內插件和TSV,以促進芯片和基板之間高速電信號的直接傳輸,不過,單片硅內插層存在良率問題。在2021年推出的CoWoS-S5里更新了對良品率模式的監測,沒有發現電阻損失或漂移。

此外,在高頻率下工作時,TSV會造成信號損耗和失真,原因是其尺寸較大(深度約為100um),所用材料也較多(埋在有損耗的硅基板內)。為了盡量減少這種影響,CoWoS-S5也重新優化了TSV,對比上上一代產品的射頻測量特性,第五代插入損耗(S21)更低,從而改善了信號完整性。

CoWoS-S5還將硅中介層擴大到3倍光罩面積,擁有8個HBM2E堆棧的空間,容量高達128GB。隨著AI芯片需求的激增,硅中間層面積的擴大卻帶來了新挑戰:12英寸晶圓切割出的中間層數量有所減少,這預示著臺積電在CoWoS產能方面將長期面臨供不應求的窘境。同時,在CoWoS技術中,GPU周邊密集布置了多個HBM,HBM數量的劇增與標準提升也使得其成為CoWoS中的關鍵瓶頸之一。

CoWoS-R

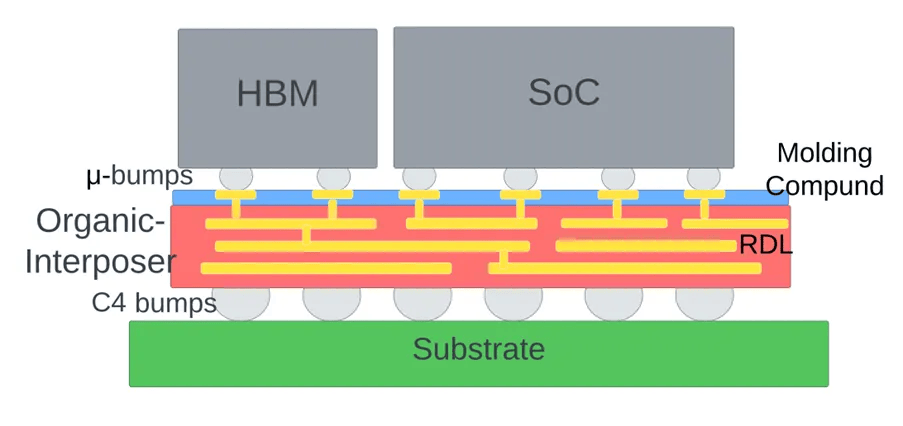

這項技術用有機中介層取代了CoWoS-S的硅插層,聚合物和銅引線構成的RDL互連器最小間距為4um(線寬/間距為2um),具有良好的信號和電源完整性性能,路由線的RC值較低,可實現較高的傳輸數據速率。與CoWoS-S相比,CoWoS-R具有更高的可靠性和成品率,RDL層和C4/UF層因SoC與相應基板之間的熱膨脹系數(CTE)不匹配而提供了良好的緩沖效果,C4凸塊的應變能量密度大大降低。

圖2:CoWoS-R封裝

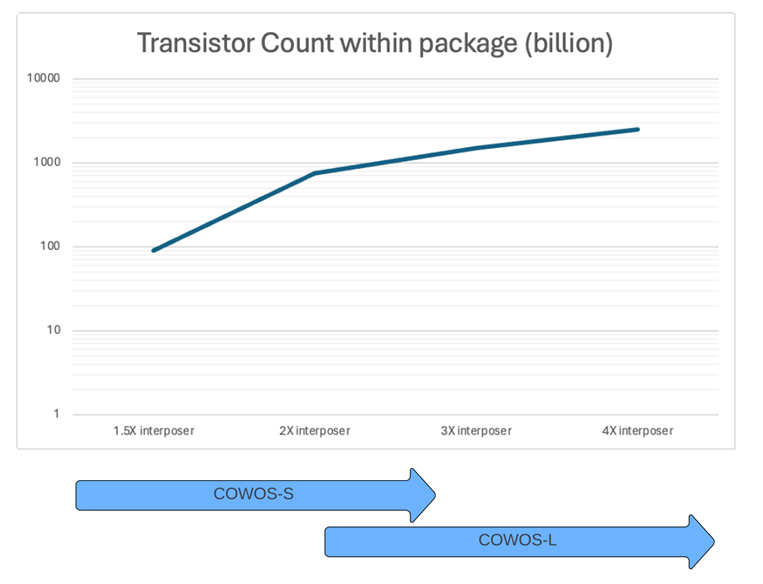

隨著算力加速卡需求持續攀升,使用CoWoS封裝技術的需求有望持續擴大。為應對產能挑戰,臺積電正著手研發CoWoS的另一版本 —— CoWoS-L。此版本有望構建出包含多達8個掩模版的系統級封裝(SiP)產品,預示著未來三年內,即便將CoWoS產能增長四倍,仍可能難以滿足市場對高性能封裝技術的旺盛需求。

CoWoS-L

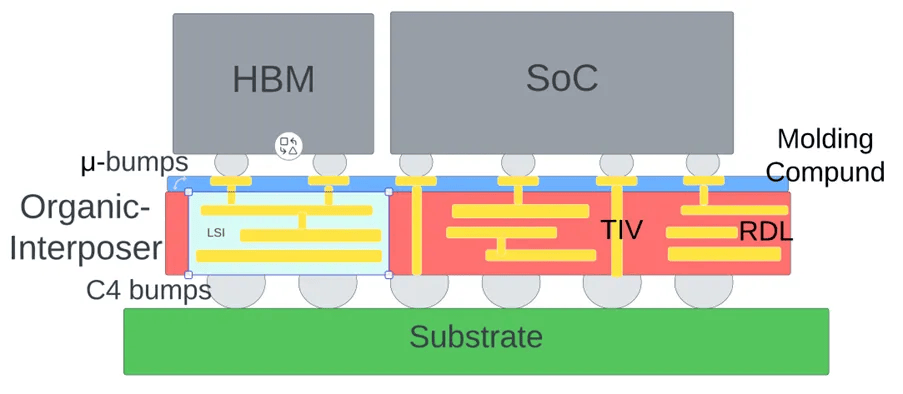

這種封裝使用LSI和RDL內插件,共同構成重組內插件(RI)。該方案采用中介層與LSI進行芯片間的互連,同時利用RDL層實現電源和信號傳輸,其特點包括能在高速傳輸中提供低損耗的高頻信號,以及能夠在SoC芯片下面集成額外的元件。

圖3:CoWoS-L封裝

除了RDL內插件外,還保留了CoWoS-S的誘人特點,即TSV。這也緩解了CoWoS-S中由于使用大型硅內插件而產生的良品率問題,在某些實施方案中,它還可以使用絕緣體通孔(TIV)代替TSV,以最大限度地降低插入損耗。除此之外,CoWoS-L技術還使用了深溝電容器(DTC),可提供高電容密度,從而提高系統的電氣性能。這些電容器可充當電荷庫,滿足運行高速計算應用時的瞬時電流需求。

與系統級芯片等老式封裝技術相比,CoWoS技術可在封裝中支持更多晶體管。所有需要大量并行計算、處理大矢量數據和需要高內存帶寬的應用都最適合使用這種技術。

CoWoS是一種2.5D/3D集成技術,與其前代產品相比,制造復雜度較高。制造復雜性直接導致采用這種封裝技術的芯片成本增加。這被認為是近來高性能計算和人工智能芯片成本增加的一個重要原因,而CoWoS的測試成本也增加了總成本。

巨頭需求激增

目前,盡管AI芯片尚未普遍采用最前沿的制造技術,但其性能的持續增強卻與先進的封裝技術密不可分。依據Yole最新發布的《2024年先進封裝狀況》報告,預計未來幾年內,先進封裝市場將保持強勁增長勢頭。從2023年至2029年,該市場的年復合增長率將達到11%,市場規模有望增長至695億美元。同時,DIGITIMES Research也指出,隨著云端AI加速器需求的不斷攀升,預計到2025年,全球對CoWoS及類似封裝產能的需求將大幅上升113%。

依托CoWoS技術,臺積電已穩坐全球封裝領先地位。隨著先進封裝業務在臺積電整體營收中占比的持續攀升,其毛利率也呈現出穩健的增長態勢。市場分析師預測,今年臺積電在先進封裝領域的收入有望沖破70億美元大關,甚至挑戰80億美元的高位。目前,先進封裝業務已占據臺積電總營收的7%至9%的份額,展望未來五年,該部門的增長速度有望超越臺積電的整體平均水平。

受供需關系影響,預計明年3nm工藝的價格將略有上調,而CoWoS技術的價格漲幅則可能達到10%至20%之間。為了應對CoWoS封裝技術產能緊張這一挑戰,臺積電在最近的歐洲技術研討會上宣布,計劃以超過60%的復合年增長率持續擴大CoWoS產能,預計到2026年底,CoWoS產能將比2023年增長四倍以上。

就目前市場來說,英偉達在2025年預計仍將是全球CoWoS先進封裝的最大需求者,預計總需求量將是臺積電全部產能的63%;而博通的需求將緊追英偉達之后,成為CoWoS先進封裝需求的第二大客戶,但所需的產能占比卻遠遠落后于英偉達,僅有13%;AMD和Marvell則是并列第三大客戶,所需的產能占比均為8%;其他客戶還包括亞馬遜AWS+Alchip占比3%、英特爾占比2%、賽靈思占比1%,其他廠商占比3%。

據TrendForce集邦咨詢最新報告披露,英偉達已將其Blackwell Ultra圖形處理單元(GPU)重命名為B300系列,計劃專注于向北美大型云服務提供商(CSP)供應采用CoWoS-L技術的GPU產品 —— 如B300或GB300等,這一戰略調整將顯著推動CoWoS-L封裝技術市場的繁榮。預計至2025年,英偉達對CoWoS-L技術的需求將激增至38萬片晶圓,相較于2024年的2萬片,增長率高達驚人的1018%。

臺積電在美國建設新廠、采用先進封裝技術以及供應鏈調整等舉措,無疑將進一步加速全球半導體產業的布局。同時,這也將為全球半導體產業的競爭格局帶來新的挑戰和機遇。

評論