亞穩態:數字電路中的"幽靈"陷阱

在電子設計領域,亞穩態問題是一個關鍵且復雜的挑戰,它影響著數字電路的穩定性和可靠性。深入理解亞穩態的發生機制及有效解決方法,是電子工程師必備的技能。本文將系統地闡述亞穩態問題,從數字電路的基本工作原理入手,逐步深入到亞穩態的產生、危害及預防措施,旨在為工程師們提供全面且清晰的亞穩態分析視角。

本文引用地址:http://www.104case.com/article/202502/466813.htm

一、CMOS器件基礎與信號傳輸特性

1.1 MOS管電容模型與信號延遲

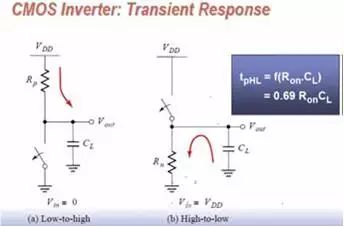

RC充放電模型:PN結電容與導通電阻構成充放電回路,RpCL與RnCL差異導致上升/下降時間不對稱

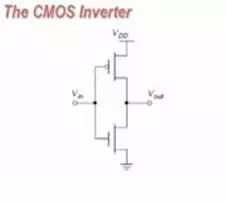

信號傳播本質:所有邏輯門存在固有傳輸延遲(典型反相器結構如圖1)

動態功耗控制:結點電容充放電決定功耗,使能控制可優化能效

CMOS 中的信息保存

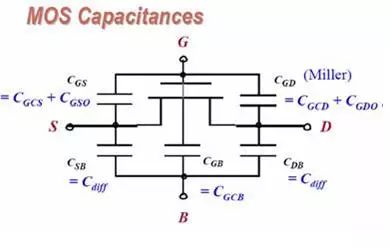

在數字電路中,CMOS 工藝晶體管的工作機制是理解亞穩態問題的基礎。當晶體管制造完成后,不同極之間因介電物質形成電容,工作時這些電容會充放電,充放電回路上的 R、C 值決定了回路的時間常數(RC)。

以 CMOS 工藝中的反向器為例,它由一個 NMOS 和一個 PMOS 組成,可簡化為工作電阻 Ron 和結點電容 CL 構成的充放電電路。當輸入為 0 時,PMOS 導通對 CL 充電,時間由 RpCL 決定;輸入為 1 時,NMOS 導通對 CL 放電,時間由 RnCL 決定。CL 由 P/NMOS 漏極結點上所有相關電容組成,這是一種近似計算方法(將分布電容集總)。

從反向器的工作原理,我們可以得出幾個重要結論:

任何信號從輸入端口傳遞到輸出端口都需要時間。

對 CL 的充放電影響系統的動態(翻轉)功耗,降低功耗可對不使用的信號添加使能。

由于 Rp!= Rn,所以 RpCL!= RnCL,即 rising time!= falling time。

對于分析亞穩態問題,關鍵是要記住信號傳輸需要時間這一點,其他門電路的分析過程與之類似。

1.2 時序器件工作機制

D鎖存器特性

電平敏感特性:使能信號有效期間直接傳遞輸入

建立過程震蕩:輸入變化引發內部反饋競爭

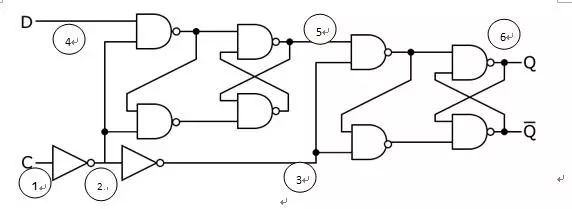

主從D觸發器架構

兩級鎖存串聯實現邊沿觸發

關鍵時序參數:

Tsetup:采樣窗口前邊界

Thold:采樣窗口后邊界

Tcko:時鐘到輸出穩定時間

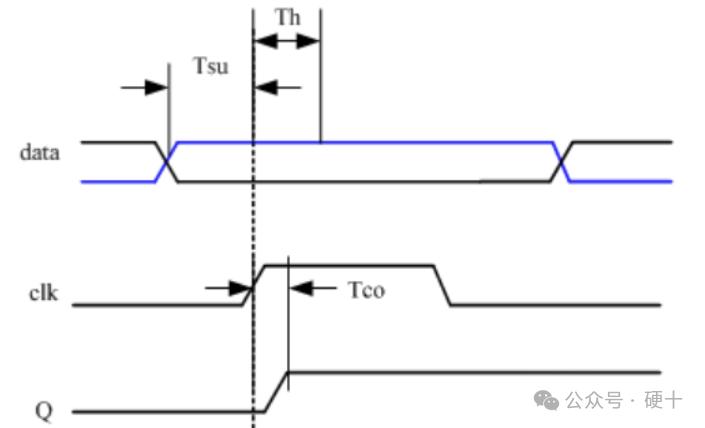

建立時間(Tsu:setup time)是指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間不夠,數據將不能在這個時鐘上升沿被穩定的打入觸發器,Tsu就是指這個最小的穩定時間。

保持時間(Th:hold time)是指在觸發器的時鐘信號上升沿到來以后,數據穩定不變的時間,如果保持時間不夠,數據同樣不能被穩定的打入觸發器,Th就是指這個最小的保持時間。

SETUP/HOLD 時間的意義

S/H 時間是時序器件的重要屬性,了解其產生機制對于理解亞穩態至關重要。

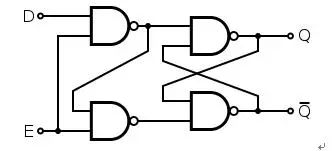

任何器件原則上都是電平有效的,邊沿觸發的器件是在此基礎上實現的一種 “把戲”。以 D 鎖存器為例,當 E 維持在高電平時,D 端輸入值 D0,該值從 D 端與非門進入器件,會有延遲,再加上反饋信號的不一致,使得 Q 端輸出電壓在建立過程中存在 “不穩定階段”,即 Setup time。這個不穩定階段的長度與器件傳輸時延、D 端輸入電平、Q 端初始電平有關(假設 E 端電平不變),起始位置在 D 開始有效的那一點。

鎖存器

上升沿有效的D觸發器(DFF)

在時序電路中常用的 D 觸發器,由 D 鎖存器等電平器件組成。以典型的上升沿有效的 D 觸發器模型為例,從時鐘端口上升沿(50%)開始,到窗口時間前面那一點結束,這段時間是 DFF 的設置時間;從時鐘端口上升沿開始,到窗口時間后面那一點結束,是 DFF 的保存時間;從時鐘端口上升沿開始,到輸出點 Q 穩定結束,是 DFF 的 clock to output 時間,可用 Tcko、Tco 表示。

通常,高速器件的時間窗口非常小。在純時序器件前端加上組合邏輯,會占用傳輸時間,導致采樣窗口相對時鐘上升沿提前,當采樣窗口尾部提前到時鐘上升沿之前時,就會出現負保持時間(設置時間永遠在上升沿前面,永遠是正的),這說明 “不純的時序器件內部的組合邏輯的傳輸時間” 大于 “純時序器件原來的保持時間的絕對值”。

從以上分析可以得出:

主從結構的時序器件的 S/H 時間和其內部第一級鎖存結構的設置時間,以及其可能含有的 Inverter 的傳輸時間有關。

主從結構的時序期間的 CKO 時間和其內部第二級鎖存結構的設置時間,以及其可能含有的 Inverter 的傳輸時間有關。

主從結構的時序器件的第一級鎖存結構的設置時間是影響其采樣窗口的主要因素,數據在這個采樣窗口被捕獲進觸發器。

任何在采樣窗口時間內的電平異常,都可能引起采樣異常,這是導致亞穩態的最根本原因。

二、亞穩態本質與觸發機制

2.1 亞穩態物理成因

中間電平鎖定:采樣窗口內輸入變化導致鎖存器進入正反饋競爭狀態

噪聲敏感性:熱噪聲可能打破平衡,導致輸出隨機化

亞穩態的產生

從器件角度看,在采樣窗口時間內,如果輸入電平不穩定,就可能導致亞穩態。以 D 觸發器為例,當 DFF 第一級的 E 關斷時,D 點的不同輸入電平會 “定格”,這個初始值會影響第一級鎖存器的設置時間或決斷時間。若初始值恰好在中間電平,第一層與非門的輸出端達到應有的電平高度所需時間會變長,加上互相反饋輸入的聯合影響,整個鎖存器的設置時間都會被拉長。

由于系統存在噪聲,加上噪聲會導致最后的電平與輸入邏輯無關。但鎖存器件有正反饋效應,初始信號越清晰,輸出信號越快設置好,受噪聲影響越小,從概率上講,決斷時間不會無限長。然而,不加控制的不穩定電平可能對后面器件的電平設置帶來不可預測的后果。

從上述分析可知:

采樣窗口越小,采樣異常的可能性越小,但隨著系統時鐘越來越快,采樣窗口所占時鐘周期的比例變化不大(數量級變化)。

保證采樣窗口內的數據絕對穩定,可完全避免亞穩態,但在有異步電路或跨時鐘域的情況下,很難做到。

亞穩態有兩種危害,即 “輸出較長時間的不穩定電平” 和 “邏輯錯誤”。

從 RTL 級來看,亞穩態的產生主要與 S/H 時間違約有關。

2.2 時序違規類型

Setup違例

組合邏輯延遲過長,數據未在采樣窗口前穩定

解決方法:降低時鐘頻率/優化關鍵路徑/流水線分割

Hold違例

組合邏輯延遲過短,新數據過早破壞前次采樣

解決方法:插入緩沖器增加路徑延遲

相同時鐘域內的亞穩態 ——S/H 時間違約

設置時間違約(setup time violation):在兩個相鄰的 DFF 中間,如果有一條很長很復雜的組合邏輯器件鏈條,從前一級 DFF 出發的數據經過很久才能在后一級 DFF 的輸入端穩定下來,甚至接近時鐘周期。當信號在采樣窗口開始之后才穩定,DFF 第一級沒有足夠時間正確設置電平,就會導致亞穩態。這種情況是由于組合邏輯傳輸時間過長引起的,設計時只需考察最長的那些路徑。

保持時間違約(hold time violation):在第一周期上升沿,從前一級觸發器出發的 D0 到達下一級(接近下一周期上升沿),此時在第二周期上升沿,從前一級觸發器出發的 D1 經過很短路徑到達下一級。若這個傳輸時間小于保持時間,D1 會在上一個 D0 還未完全結束采樣時破壞采樣,從而產生保持時間違約。這種情況是由于組合邏輯傳輸時間過短引起的,設計時只需考察最短的那些路徑。

針對 S/H 時間違約的預防辦法:

設置時間違約:這是 ASIC 時序分析中的主要問題。若從最長路徑上傳來的信號到達太晚,錯過采樣窗口,可采取以下措施:

增加時鐘周期長度,但會導致整體速度下降,一般不采用。

重新分配關鍵路徑,將過長路徑中的一部分組合邏輯分離出來,放到相鄰時序級或單獨形成一級(如 CPU 中的多級流水技術),前提是不破壞邏輯功能和系統功能。

若上述方法不可行,只能從組合邏輯的結構上下手,調整結構。

保持時間違約:處理方法是讓信號更晚到達下一級輸入端口,以防止對上一個數據造成影響。通常的做法是在傳輸路徑上增加 buffer,buffer 由兩個反相器構成,不影響邏輯功能,只增加延遲。當信號線過長時,buffer 還可增強輸出端的驅動能力,分割長信號線進行 “分段驅動”。

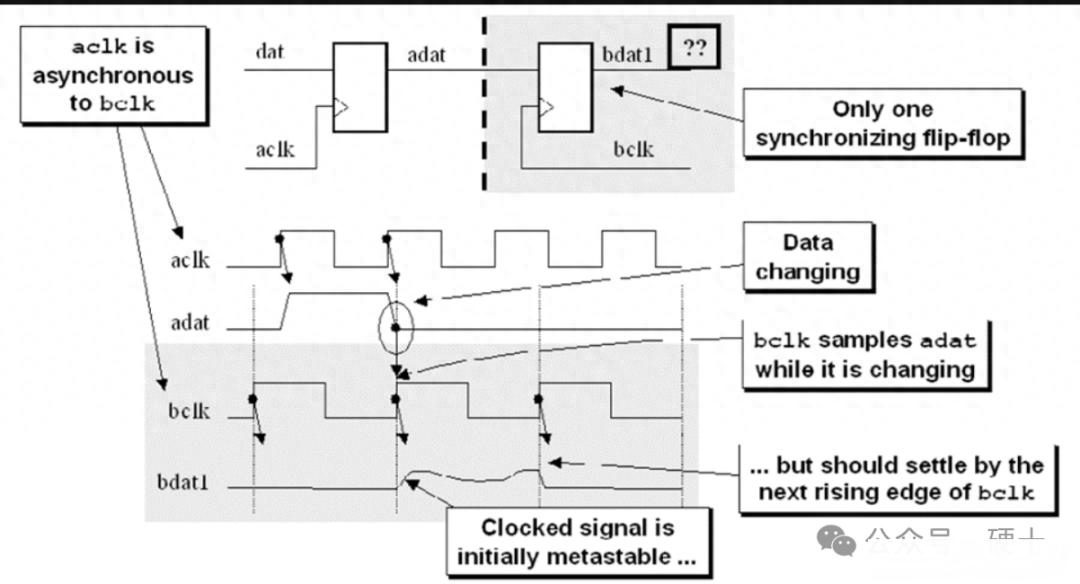

時鐘相位/頻率無確定關系導致采樣窗口隨機重疊

MTBF模型:失效率=時鐘頻率×數據變化率×e^(-Tr/τ)

同步器:將幾個用本地時鐘驅動的時序器件串聯起來采樣輸入的異步數據。當第一級時序器件出現亞穩態時,其輸出的不穩定中間值在第二級采樣窗口到來時,仍處在可使第二級出現亞穩態的電平范圍內的概率會變小,若再加上第三級,這個概率幾乎可忽略不計。多個時序器件串聯,總概率是各自概率的積,可降低不穩定時間,使輸出電平穩定時間接近時鐘周期。但邏輯上無法消除亞穩態的影響,MTBF = 1/(失效率 1× 失效率 2×…× 失效率 n),兩個 DFF 串聯時,基本可保證 MTBF 很大。此方法用于控制信號時,若采樣失效可多等待幾個周期保證有效采樣;用于數據信號時,很難保證無差錯傳輸。

異步 FIFO 與握手協議:用于傳輸對傳輸質量要求較高的數據信號,主要用在跨時鐘域傳輸中。異步 FIFO 是一種總線思維,結構相對簡單;握手協議是一種邏輯方法,與 TCP 握手類似。

延遲鎖定環 Delay locked loop(DLL):在跨時鐘域傳輸模式下,通過統計交界面上信號的有效時間與發送源時鐘信號周期的相對關系,將目的地時鐘信號與發送源時鐘信號的延遲關系進行鎖定,保證在目的地的采樣周期永遠在信號有效的時間范圍內,實現兩個非同步時鐘的同步。

異步復位同步釋放:復位撤銷時通過本地時鐘同步

復位毛刺濾波:施密特觸發器整形

由于亞穩態的出現是概率現象,為便于估算其危害程度,提出了 “平均無故障時間” MTBF,MTBF = 1 / 失效率。

三、跨時鐘域同步挑戰

3.1 異步接口風險

對于相同時鐘域內的時鐘樹,不同點存在相位差別,可通過計算時鐘信號線長度進行預測,并通過時鐘域內的時鐘樹綜合算法求得優化結構,相對較好解決。

對于跨時鐘域通信和異步同步通信,情況更為復雜。跨時鐘域是一種異步同步通信,兩個時鐘域內的時鐘沒有必然的頻率和相位關系。工程上采用 “各自獨立分析優化,在此基礎上進行互相通信設計”。

同步異步交界面的亞穩態

在同步異步交界面或跨時鐘域的交界面上,外部發來的數據到達時間與本地時鐘很難產生必然的時序關系,即外部數據在本地輸入端口的穩定時間與本地時序器件的采樣窗口在時序上沒有必然聯系,從而導致亞穩態問題。

解決此問題的關鍵是保證本地時序器件的采樣窗口內所接受到的數據是絕對穩定的,但這極其困難。對于異步同步交界面,異步數據與本地同步信號無聯系,原則上無法保證穩定采樣;對于跨時鐘域的交界面,兩個時鐘的相位和頻率無必然聯系,同樣原則上無法保證穩定采樣。

常用的解決辦法如下:

四、特殊場景亞穩態防護

4.1 復位信號處理

復位信號由于是在隨機狀態下產生的,對系統的影響及分析過程與異步同步交界面的亞穩態問題類似。當理解亞穩態的形成機制后,再理解復位信號可能導致的亞穩態問題就變得非常簡單。

總結

亞穩態產生的主要原因是在時序器件的采樣窗口內,無法保證輸入信號始終保持在一個穩定的電平上。為解決亞穩態問題,我們可通過減小采樣窗口來增加采樣成功率(如使用邊沿觸發器件),或通過對采樣窗口或輸入數據的穩定窗口的 “移動” 來保證采樣成功。但在有異步信號參與時,問題的解決變得異常復雜,目前還沒有一種通用、有效、可行的解決方法。然而,通過深入探討亞穩態形成機制,我們能夠從工程角度更好地解決實際項目中可能出現的具體亞穩態問題。

在電子設計中,亞穩態問題的解決需要綜合考慮電路結構、信號特性和系統要求等多方面因素。通過不斷深入研究和實踐,工程師們能夠在面對亞穩態挑戰時,做出更合理的設計決策,確保數字電路系統的穩定可靠運行。

評論