VHDL實現PCM碼解調程序模塊設計

3.2 字節同步信號產生程序

設b為一個標志位,當b為‘1’時,表示檢測到請求信號的上升沿且尚未結束一幀傳輸,該進程的byte為字節同步信號,用來標志一個字節接收完畢。字節同步信號產生程序仿真圖如圖5所示。

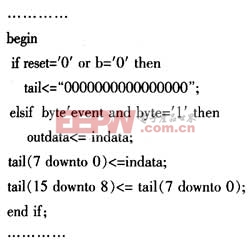

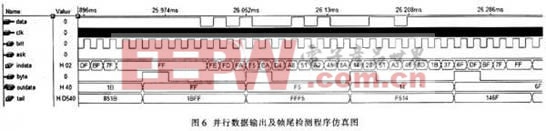

3.3 并行數據輸出及幀尾檢測程序

并行數據在字節同步信號byte的上升沿輸出,outdata為并行數據輸出端,同時將并行數據賦值給幀尾標志tail的低8位,將tail的低8位給其高8位,當tail的值為146F時,即表示一幀結束。并行數據輸出及幀尾檢測程序仿真圖見圖6。

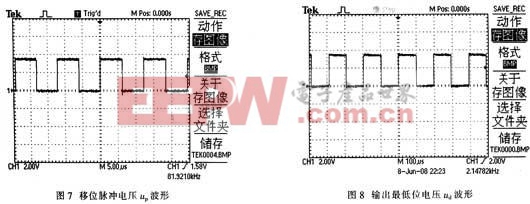

4 調試結果

所發送數據是以00H為起始遞增的一串數據,該數據字長200,結尾以146F為標記。調試過程中,南示波器觀察波形,可以看到請求信號的頻率及脈寬、移位脈沖的頻率均符合要求,解調出的并行數據與數據源的數據相吻合。圖7和圖8分別給出移位脈沖電壓up波形和輸出最低位電壓ud波形。

5 結語

基于FPGA的PCM碼解調電路VHDL程序模塊設計,可使電路在發出請求脈沖后,在移位脈沖的作用下,同步接收PCM數據,并輸出8位并行數據,在幀尾處結束解調。通過仿真及最終電路調試驗證了該系統設計能夠實現PCM碼解調系統功能。

評論