基于FPGA的可層疊組合式SoC原型系統設計

對于JTAG信號,TMS和TCLK是共用信號,所以JTAG控制模塊主要控制TDI和TDO的連接關系。其中Top_enable信號由板卡外部輸入,當有板卡連接時,Top_enable有效,否則為無效。Bottom_enable信號由板卡上撥碼開關控制。

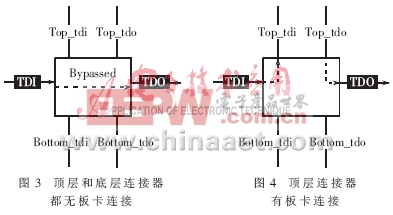

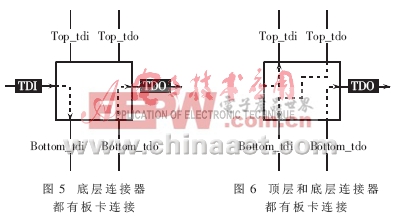

當頂層連接器和底層連接器都不接外部板卡時, JTAG控制器模塊內部連接關系如圖3所示,即Bypassed模式。當頂層連接器上有板卡連接時,Top_enable有效,JTAG鏈要經過頂層的板卡環路到主板,JTAG控制器模塊內部連接關系如圖4所示。

如果底層連接器上有板卡連接,則Bottom_enable有效,JTAG鏈要經過底層的板卡環路到主板,JTAGController模塊內部連接關系如圖5所示。如果頂層和底層的連接器上都有板卡連接,即top_enable和Bottom_enable都有效,JTAG鏈要經過頂層和底層的板卡再環路到主板,JTAGController模塊內部連接關系如圖6所示。

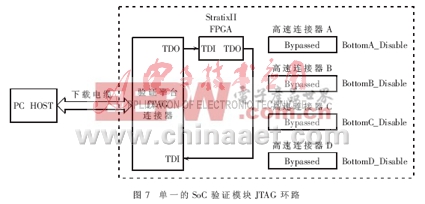

整個SoC驗證模塊上共有4組這樣的連接器,每組連接器都有各自的JTAG控制器。

2 SoC原型模塊層疊方法

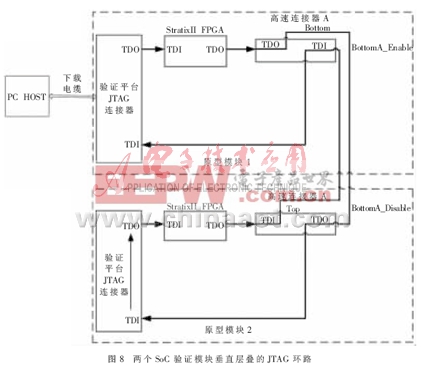

單FPGA的方案無法滿足驗證所需要的邏輯規模,可以采用多個模塊層疊組合的方式來構建更大規模的SoC驗證系統。借助EDA軟件,如Synplify公司的Certify軟件,可以將規模較大的RTL設計劃分成多個模塊,分別下載到多個FPGA上實現驗證。這就要保證層疊組合在一起的多個板卡上FPGA的JTAG鏈相互連接構成一個完整的回路,實現配置和測試的一致性。

沒有任何層疊擴展的SoC原型模塊JTAG環路如圖7所示,原型模塊的JTAG連接器通過下載電纜和PC主機的EDA軟件聯通起來。板上的JTAG信號經過FPGA主芯片后,閉環反饋給PC主機。板上4組連接器沒有連接任何板卡,因此都是Bypassed模式。

2.1 垂直層疊模式

垂直層疊模式是將SoC原型模塊邊沿對齊,垂直堆疊連接起來。每個FPGA都可以通過4個連接器與其他FPGA通信,共享最多480個IO管腳。這種模式支持2~4個原型模塊層疊,可以滿足絕大多數的應用。以兩個原型模塊垂直層疊為例,其JTAG環路示意圖如圖8所示。其中,原型模塊1位于原型模塊2的上方,通過高速連接器A來實現JTAG鏈閉合回路。由于模塊1的A組底層連接器與模塊2的A組頂層連接器相連,因此模塊1的Bottom_Enable開關要設置為使能狀態。

評論