利用基于SystemC/TLM的方法學進行IP開發和FPGA建模

隨著系統級芯片技術的出現,設計規模正變得越來越大,因而變得非常復雜,同時上市時間也變得更加苛刻。通常RTL已經不足以擔當這一新的角色。上述這些因素正驅使設計師開發新的方法學,用于復雜IP(硬件和軟件)以及復雜系統的驗證。ST公司建立了一個設計流,它從高級抽象開始,易于將模型寫入IP的精密周期或RTL模型中。當轉入低級抽象時,建模變得復雜,故IP驗證也復雜。我們的方案最適合于這種應用場景,因為它允許人們在各地相似的環境中運行相同的測試平臺和測試場景,因而允許在整個開發周期里高效地復用所有的測試范例和環境。

本文引用地址:http://www.104case.com/article/191821.htm在半導體領域,開發產品的第一步就是以高級抽象開發規范的模型,通常用C/C++來實現。這里,SystemC和C++庫提供了很大幫助。它簡化了共存的硬件和軟件設計的概念化。再加上實現事務級模型間對口連接的TLM傳送庫,SystemC加速了整個驗證過程。另一個重要方面是所有不同抽象架構中經過增強的可移植性。同一測試配置可以無縫地用于不同抽象級的設計。

本文將討論一種此類的方法學。最終的目標是設計和實現UWB MAC(媒體訪問層)IP。出于架構開發的目的,決定用SystemC來實現整個IP。還開發了抽象級具有不同程度變化的不同架構。所付出的努力比較少,最后得到的仿真速度很快,軟件的實際編寫也可以在設計周期非常早的階段開始。該IP的RTL結果被移植到了SPEAr系列的FPGA中。除了ARM內核和相應的一系列IP,SPEAr還提供一個可配置邏輯塊,這為用戶在實現其邏輯功能時提供了無與倫比的靈活性。從而縮短了上市時間,同樣也實現了空前的成本節省。

設計開發方法學

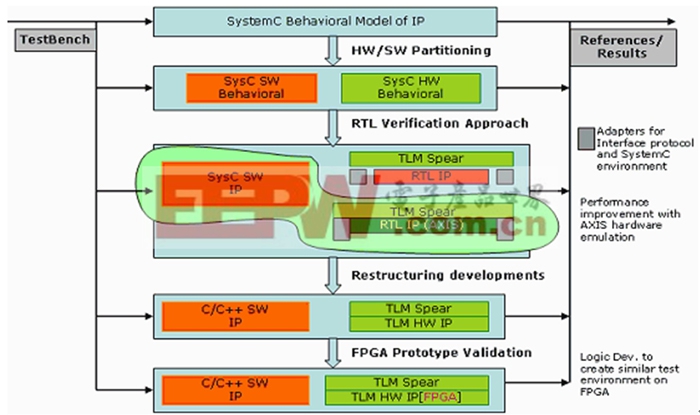

圖1所示的該方法學實現了開發的內核中的事務級建模(TLM)。TLM是一種對數字系統進行建模的高級方案,這里將模塊之間的具體通信與功能單元或通信架構的具體實現分離開。把總線或FIFO這類通信機制模型化成信道,用SystemC接口類將這些信道提供給模塊和部件。這些信道模型的信令接口功能將取代事務請求,這將減少具體的低級信息交換。

圖1:IP開發方法學流程。

評論