FPGA芯片在高速數據采集緩存系統(tǒng)中的應用

3.2大容量FIFO數據緩存模塊

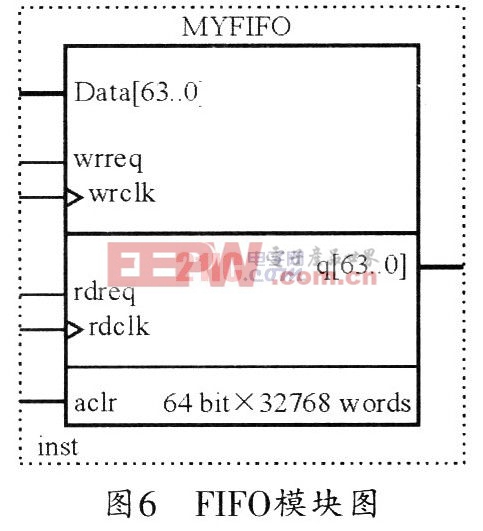

由于采集的雷達信號數據量很大,所以,本系統(tǒng)通過Quartus中軟件自帶的宏功能MegaWizardPlag_in Manager來產生一個64bitx32768-words的大容量FIFO,從而有效地利用了這片FPGA的存儲資源。其產生的FIFO模塊如圖6所示。本文引用地址:http://www.104case.com/article/191754.htm

圖6中,64位數據由ADC的高速數據采樣提供,ADC的I、Q兩路數據均為16位寬。為了獲得更高的速度以及更大的數據緩存量。在數據進入

FIFO之前,可對ADC的采樣數據進行數據抽取和拼接,以將兩組32位寬的IQ數據拼接成64位寬數據,然后一次送入FIFO中進行緩存。FIFO的wrreq寫使能信號由前面提到的視頻檢測脈沖以及DSP的控制信號共同提供,其中寫時鐘wrclk與ADC數據拼接時鐘同步,讀時鐘rdclk與DSP時鐘同步,FIFO數據出口與DSP總線相連接。

系統(tǒng)的其他配置以及外圍接口由于不是本文的重點,在此省略不講。

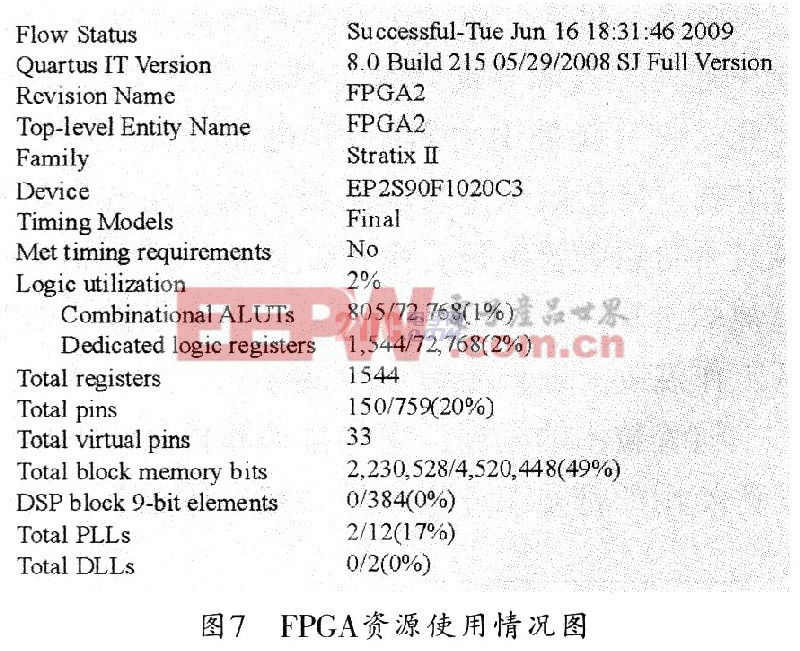

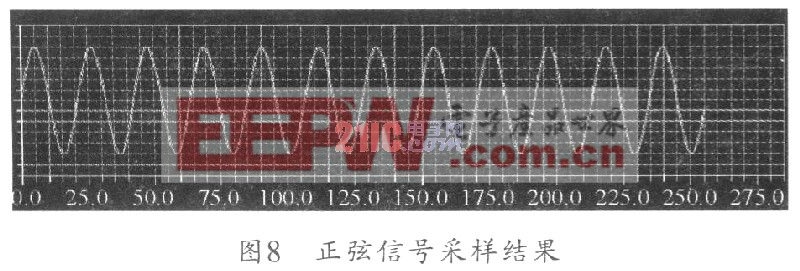

在Quartus平臺下進行時鐘分配、三線串口配置等相關處理,以及信號處理模塊綜合后,所得到的系統(tǒng)資源使用情況如圖7所示。然后再利用VisualDSP++5.0平臺讀取采樣信號數據,并用plot進行繪圖,即可得到如圖8所示的高速采樣結果圖。

4 結束語

本文是在參與實際項目的基礎上完成的,本系統(tǒng)目前已經應用于某雷達信號處理機中。隨著高速器件的開發(fā)和利用,數字接收機技術的迅速發(fā)展,其信號采集與處理的速度必將更快,處理質量會更好,處理數據量也會更大。

評論