基于FPGA的偽隨機序列發生器設計

摘要:討論了應用移位寄存器在Ahera的FPGA芯片中實現線性和非線性偽隨機序列的方法,該算法基于m序列本原多項式來獲得線性m序列和非線性m子序列移位寄存器的反饋邏輯式。文中給出了以Altera的QuartusⅡ為開發平臺,并用VHDL語言實現的m序列的仿真波形。

關鍵詞:偽隨機序列;m序列;m子序列;移位寄存器;VHDL語言編程

0 引言

偽隨機序列現已廣泛應用于密碼學、擴頻通訊、導航、集成電路的可測性設計、現代戰爭中的電子對抗技術等許多重要領域。偽隨機序列的偽隨機性表現在預先的可確定性、可重復產生與處理。偽隨機序列雖然不是真正的隨機序列,但是當偽隨機序列周期足夠長時,它便具有隨機序列的良好統計特性。在已有的序列中,m序列的應用最為成熟和廣泛,為此,本文給出線性m序列和基于m序列的非線性m子序列的FPGA實現方法。由于FPGA的內部邏輯功能是通過向內部靜態存儲器單元加載配置數據來實現的,其配置文件決定了邏輯單元的邏輯功能以及模塊間或與I/O間的連接,故可最終決定FPGA實現的功能。FPGA的這種結構允許多次編程,并享有快速有效地對新設計進行優化的靈活性,為此,本文選用了altera的cyclone系列FPGA芯片。EPlCl2-240PQFP,該芯片內部有12060個邏輯單元、239616 bit RAM、兩個鎖相環(PLL)。本文應用移位寄存器理論來產生序列,其算法的關鍵是找到線性m序列和非線性m子序列移位寄存器的反饋邏輯式。

1 m序列的實現

1.1 基于FPGA的m序列實現

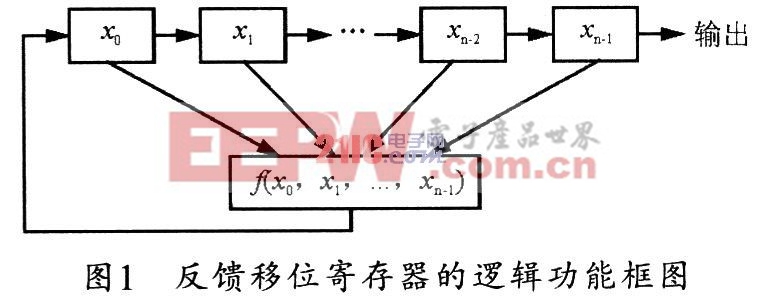

利用反饋移位寄存器產生0、1序列時,其n位反饋移位寄存器的邏輯功能如圖1所示。

圖中,xi表示寄存器所處的狀態,通常用0和1來代表兩個可能的狀態,并且把0和1看成是有限域GF(2)的兩個元素。f(x0,x1,…,xn-1)刻劃了移位寄存器反饋邏輯的功能,它可以看成一個定義在GF(2)上并且在GF(2)中取值的n元函數,當f(x0,x1,…,xn-1)可以表示成一線性齊次函數時,即 GF(2),相應的反饋移位寄存器是線性的,而由線性移位寄存器產生的序列就稱為線性移位寄存器序列。m序列就是線性移位寄存器序列。

GF(2),相應的反饋移位寄存器是線性的,而由線性移位寄存器產生的序列就稱為線性移位寄存器序列。m序列就是線性移位寄存器序列。

評論