基于VHDL語言的幾種消抖電路的設(shè)計(jì)

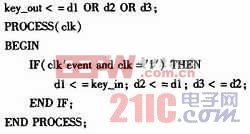

主要程序結(jié)構(gòu)如下:

圖4為D觸發(fā)器型消抖電路波形仿真圖,由圖可見,當(dāng)按鍵操作時(shí)間大于或等于clk時(shí)鐘周期的3倍時(shí),輸出一個(gè)正脈沖,正脈沖的寬度比key_in少2個(gè)clk時(shí)鐘周期。本文引用地址:http://www.104case.com/article/191239.htm

D觸發(fā)器型消抖電路與計(jì)數(shù)器型消抖電路(一)相似,計(jì)數(shù)器型消抖電路(一)輸出脈沖寬度是固定的,D觸發(fā)器型消抖電路輸出脈沖寬度隨著按鍵操作時(shí)間長(zhǎng)短變化。

3 狀態(tài)機(jī)型消抖電路

狀態(tài)機(jī)型消抖電路采用有限狀態(tài)機(jī)的設(shè)計(jì)方法來描述與實(shí)現(xiàn),狀態(tài)機(jī)有S0,S1,S2三種狀態(tài),在S0狀態(tài)下key_out輸出為低電平,并以clk時(shí)鐘信號(hào)的頻率采樣按鍵輸入信號(hào),如果key_in=‘0’,則保持在S0狀態(tài),并繼續(xù)采樣按鍵輸入信號(hào)的狀態(tài),如果key_in=‘1’,則轉(zhuǎn)入S1狀態(tài);在S1狀態(tài)下key_out輸出仍為低電平,繼續(xù)采樣按鍵輸入信號(hào)的狀態(tài),如果key_in=‘1’,則轉(zhuǎn)入S2狀態(tài),如果key_in=‘0’則轉(zhuǎn)入

S0狀態(tài);在S2狀態(tài)下繼續(xù)采樣按鍵輸入信號(hào)的狀態(tài),如果key_in=‘1’,則保持在S2狀態(tài),key_out輸出正脈沖,如果key_in=‘0’,則轉(zhuǎn)入S0狀態(tài),key_out輸出低電平。

主要程序結(jié)構(gòu)如下:

圖5為狀態(tài)機(jī)型消抖電路波形仿真圖,由圖可見,該狀態(tài)機(jī)型消抖電路與D觸發(fā)器型消抖電路仿真結(jié)果一致。

4 結(jié)束語

采用VHDL語言實(shí)現(xiàn)按鍵的消抖電路的方法有很多,本文介紹的幾種消抖電路都通過仿真分析及實(shí)驗(yàn)驗(yàn)證,消抖效果良好,性能穩(wěn)定,而且各有自己的優(yōu)勢(shì)與缺點(diǎn),設(shè)計(jì)者可以根據(jù)設(shè)計(jì)需求選擇使用。

評(píng)論