基于Nios II處理器的SVPWM IP Core設(shè)計

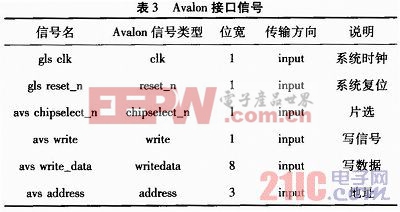

(2)Avalon接口設(shè)計。

Avalon接口為SVPWM IP Core提供了一個標準的Avalon從端口,通過此接口按照Avalon從端口的傳輸協(xié)議對IP Core進行控制,相關(guān)的Avalon接口信息如表3所示。本文引用地址:http://www.104case.com/article/190673.htm

(3)乘法因子計算模塊。

這里的乘法因子是指式(6)和式(7)中的方括號內(nèi)運算的結(jié)果。本模塊根據(jù)外部A/D轉(zhuǎn)換的結(jié)果、設(shè)定的TPWM及預(yù)期的參考電壓矢量的數(shù)值,計算出式(6),式(7)的方括號內(nèi)的結(jié)果,用于乘法模塊中對ta和tb的計算。

(4)數(shù)據(jù)存儲模塊。

sinθ及sin(π/3-θ)在擴大255倍后,分別作為高8位和低8位存儲在容量為128×16 bit的ROM中,從而可以同時讀取分別用于式(6)中tb和式(7)中ta的計算。時序控制ROM的容量為32×3 bit,存儲表1中的開關(guān)時序,其高3位地址用于對6個扇區(qū)編碼,最低2位地址用于某區(qū)間內(nèi)的時序控制,由于在同一區(qū)間中采用升降計數(shù),根據(jù)表1中橋臂開關(guān)切換的對稱性可知,只要兩位地址即可存儲時序控制信號。

(5)數(shù)據(jù)選擇器。

當0≤θπ/6時,利用正弦值存儲模塊輸出數(shù)據(jù)的高8位計算tb,利用低8位計算ta;而當θ值為π/6≤θπ/3時,則應(yīng)該利用低8位計算tb,利用高8位計算ta。通過數(shù)據(jù)選擇器實現(xiàn)高、低8位的交換。

(6)時序控制模塊及IGBT時序控制ROM。

時序控制模塊根據(jù)當前所處的扇區(qū)、ta、tb及當前PWM的計數(shù)值生成IGBT時序控制ROM的地址。IGBT時序控制ROM中存儲的是橋臂開關(guān)控制的時序,根據(jù)時序控制模塊輸出的地址,將存儲在ROM中的開關(guān)控制量讀出后送至死區(qū)發(fā)生器模塊。

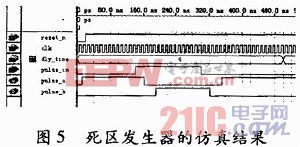

(7)死區(qū)發(fā)生器模塊。

死區(qū)發(fā)生器模塊用于將橋臂上部IGBT管的3個時序控制信號,變?yōu)橛脩粼O(shè)定死區(qū)時間的3組信號,對6個IGBT管進行控制,死區(qū)時間在0~6.3μs之間設(shè)置,步進值0.1μs。死區(qū)發(fā)生器仿真結(jié)果如圖5所示,輸入信號為pulse_in,輸出信號為pulse_a和pulse_b,死區(qū)時間設(shè)置為0.4μs。

3 設(shè)計驗證

各模塊設(shè)計完成后,用原理圖方式完成系統(tǒng)設(shè)計如圖4所示,在SOPC Builder中將之作為自定義組件添加到系統(tǒng)中生成IP Core。設(shè)計驗證在Altera公司的DE2開發(fā)板上進行,將該IP Core添加到SOPC工程中,編譯、下載到FPGA芯片中,運行測試程序后,利用SignalTapII Logic AnMyer捕捉到橋臂上方3個IGBT管的控制信號如圖6所示。圖中的sector是為方便測試而引出的扇區(qū)編號信號,由圖可知設(shè)計正確。

4 結(jié)束語

設(shè)計了一個結(jié)構(gòu)簡單、性能良好的SVPWM IP核,并在Nios II平臺下將其封裝成一個模塊化的獨立元件,使之易于在其他的工程中復(fù)用,利用該IP核可以方便地構(gòu)建基于Nios II嵌入式處理器的SVPWM控制系統(tǒng),體現(xiàn)了SOPC嵌入式系統(tǒng)的靈活性和擴展性。

評論