無(wú)分裂結(jié)構(gòu)的二維小波變換圖片處理芯片設(shè)計(jì)與驗(yàn)證

1.3.2 列變換結(jié)構(gòu)

列變換時(shí),假設(shè)第m行的第n列完成行變換后的數(shù)據(jù)為X(m,n),將該數(shù)據(jù)寄存在寄存器D1中,下個(gè)時(shí)鐘沿來(lái)臨時(shí),F(xiàn)IFO-A和FIFO-B中分別釋放出第m-1和m-2行的第n列的數(shù)據(jù)X(m-1,n)和X(m-2,n),同D1中X(m,n)數(shù)據(jù)共同完成預(yù)測(cè)步驟生成Y(m,n)并寄存在D2中,同時(shí)從D1和FIFO-A,F(xiàn)IFO-B中釋放出的數(shù)據(jù)X(m,n),X(m-1,n)和X(m-2,n)分別寄存進(jìn)FIFO-A,F(xiàn)IFO-B,F(xiàn)IFO-C。再下一個(gè)時(shí)鐘沿來(lái)臨時(shí),完成第m行第n+1列的行變換,并寄存在D1中,之后即可按照上述步驟完成第m行第n+1列數(shù)據(jù)的預(yù)測(cè)和更新,得出結(jié)果Y(m,n+1)。當(dāng)FIFO把第m行數(shù)據(jù)完全釋放出時(shí),已在該FIFO寄存了第m+1行的完整數(shù)據(jù),可以開(kāi)始下一行的列變換。同理,完成預(yù)測(cè)步驟的數(shù)據(jù)寄存在D2,F(xiàn)IFO-D,F(xiàn)IFO-E中,依據(jù)預(yù)測(cè)步驟相似的原理完成更新步驟。之后依據(jù)數(shù)據(jù)的列地址的奇偶,選擇不同的Y值輸出。

1.4 控制結(jié)構(gòu)

一般的變化模塊,均采用狀態(tài)機(jī)的控制方法,利用狀態(tài)的跳轉(zhuǎn),來(lái)控制行變化和列變化之間的關(guān)系,完成預(yù)測(cè)和更新步驟。

而本文提出了全新的、更為靈活的直角坐標(biāo)系控制法,即利用行坐標(biāo)(row-c)和列坐標(biāo)(col-c)形成一個(gè)二維直角坐標(biāo)系,并將圖片映射到直角坐標(biāo)系上,每一對(duì)坐標(biāo)(row-c,col-c)對(duì)應(yīng)直角坐標(biāo)系上圖片的一個(gè)點(diǎn),也對(duì)應(yīng)該點(diǎn)的變換時(shí)刻。通過(guò)row-c,col-c的值來(lái)判斷正在進(jìn)行變換的行列值,來(lái)決定FIFO和變化模塊的動(dòng)作。利用row-c,col-c的末位來(lái)判斷進(jìn)行變換的行和列地址分別是奇數(shù)地址還是偶數(shù)地址,決定是進(jìn)行預(yù)測(cè)步驟還是更新步驟。結(jié)合計(jì)數(shù)器,通過(guò)輸入的圖片的行像素值M和列像素值N,分別控制row-c和col-c的跳變。因而可以簡(jiǎn)單的通過(guò)改變M,N值的大小來(lái)改變進(jìn)行變換的圖片的大小。

2 結(jié)果驗(yàn)證

2.1 采用軟硬件協(xié)同驗(yàn)證的結(jié)構(gòu)

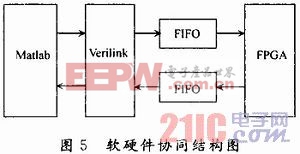

本文采用軟硬件協(xié)同工作的結(jié)構(gòu),如圖5所示。利用計(jì)算機(jī)端的Matlab軟件從FPGA芯片中讀取變換后的RGB數(shù)據(jù),并顯示在計(jì)算機(jī)顯示器上。本文引用地址:http://www.104case.com/article/190283.htm

具體結(jié)構(gòu)是將圖片數(shù)據(jù)通過(guò)北翰科技公司的Verilink插件,從Matlab軟件中送入FPGA芯片中的FIFO,小波變換模塊從FIFO中依次讀取數(shù)據(jù),并進(jìn)行變換,完成變換的數(shù)據(jù)通過(guò)FIFO送回Matlab軟件,并顯示在計(jì)算機(jī)的顯示器上。

2.2 驗(yàn)證結(jié)果

本文采用128×128像素RGB圖片作為變換圖像源,在計(jì)算機(jī)的Matlab軟件中,將圖片轉(zhuǎn)換成一維數(shù)據(jù)流,并依次通過(guò)Verilink插件送入FPGA芯片的FIFO中,在送入數(shù)據(jù)的同時(shí),F(xiàn)PGA中的變換模塊從FIFO中讀出數(shù)據(jù)進(jìn)行變換,并將變換結(jié)果通過(guò)輸出的FIFO送至計(jì)算機(jī)端的Mat lab軟件。在完成全部數(shù)據(jù)變換后,在計(jì)算機(jī)端將獲得的數(shù)據(jù)重新排列,并轉(zhuǎn)換成128×128×3的RGB圖片格式,并對(duì)比顯示變換前和變換后的圖片效果。變換前圖片如圖6(a),變換并重排后圖片如圖6(b),圖片數(shù)據(jù)高頻分量和低頻分量分離正確無(wú)誤。

3 結(jié)語(yǔ)

本文提出了無(wú)分裂步驟的小波變換結(jié)構(gòu),簡(jiǎn)化了變換模塊的控制系統(tǒng),采用數(shù)據(jù)流模式輸入數(shù)據(jù),并且和軟硬件協(xié)同的工作方式良好配對(duì),利用FPGA和計(jì)算機(jī)完成了二維小波變換的板級(jí)驗(yàn)證。本文提出的結(jié)構(gòu)在5/3小波變換中有效運(yùn)行,并起到簡(jiǎn)化結(jié)構(gòu)的關(guān)鍵作用,下一步將嘗試把該結(jié)構(gòu)運(yùn)用于9/7小波變換的硬件結(jié)構(gòu)實(shí)現(xiàn)中,并提出適合9/7小波變換硬件實(shí)現(xiàn)的結(jié)構(gòu)。

評(píng)論