為系統設計人員提供的DRAM控制器

DRAM控制器藏在您的系統核心芯片系統(SoC)中——可能有兩個,甚至是四個。有一些精心制作的邏輯小模塊,用于連接SoC內部和外部DRAM,它們并沒有引起系統設計人員的注意。它們有可能造成很大的問題,浪費帶寬,占用太多的能耗,甚至導致數據被破壞。

本文引用地址:http://www.104case.com/article/189777.htmDRAM控制器能否正常工作會使得系統有很大的不同,有的系統能夠滿足其設計要求,而有的系統則運行緩慢,過熱,甚至失敗。不論哪種情況,最終是由系統設計團隊承擔責任,他們一般很少掌握控制器的信息。

成功還是失敗都源自我們要求DRAM控制器所做的工作。模塊不僅僅是一個接口。在高級系統設計中,DRAM控制器必須很好的處理SoC體系結構復雜而又難以預測的存儲器申請,以及一側的系統軟件申請,還有另一側DRAM芯片設計復雜的時序和約束要求。能否處理好這些關系會在多個方面影響DRAM吞吐量:這很容易在系統性能上體現出來。

為解釋這些問題——以及系統設計人員能夠對此做什么,我們需要回答三個主要問題。首先,我們應檢查DRAM芯片提出的要求。然后,需要討論SoC體系結構對存儲器訪問模式的影響,第三,研究一個高級DRAM控制器的結構和功能。通過這三部分,我們得出系統設計的一些結論。

DRAM需要什么

系統規劃對外部存儲器的要求是確定性隨機訪問:任何時候來自任何位置的任意字,具有固定延時。但是,確定性隨機訪問恰恰是現代DDR3 DRAM所不能提供的。

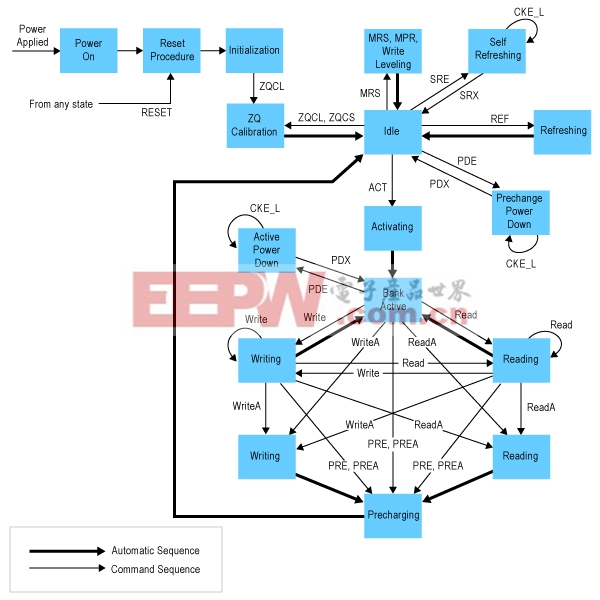

相反,DRAM提供任何您需要的字,但是具有復雜的時序約束,因此,很難知道數據究竟什么時候出現。 圖1 中“簡化的”狀態轉換圖簡單解釋了為什么會這么復雜。這種復雜度也意味著,命令到達DRAM芯片的順序會對時序以及帶寬有很大的影響。要理解這一點,我們需要深入了解DDR3 DRAM。

圖1.DDR DRAM芯片“簡化的”狀態圖顯示了控制器設計人員所面臨的復雜問題。

DRAM芯片將數據存儲在電容陣列中。當您讀寫數據時,您并不會直接訪問陣列。而是在讀寫之前,您激活陣列中的某一行。激活命令使得DRAM讀取該行中的所有列的所有比特,將其送入傳感放大器塊,它實際上用作該行的本地寄存器文件。然后,您可以對傳感放大器上的數據發出讀寫命令。通過這種方式,能夠非常快的讀寫已經激活的行:一般是三到五個時鐘來開始一次突發傳送,然后,在突發期間傳送每個字節需要一個時鐘。例如,這種時序安排使得DDR3 DRAM非常適合L2高速緩存數據交換。

但是,如果您不使用已經激活的行,那么會非常復雜。改變行時,即使是一個字節,您也必須對當前行去激活,然后激活一個新行。這一過程需要確定已經在一段時間內激活了當前行。由于讀取DRAM單元是破壞性的,因此需要最小延時:您激活了一行后,DRAM實際上是將最新到達傳感放大器上的數據復制回比特單元陣列中,然后刷新行。您可以在此期間讀寫當前行,但是,要確定在您改變行之前完成了這一過程。

評論