優化封裝以滿足SerDes應用鍵合線封裝規范

提高TDR 性能

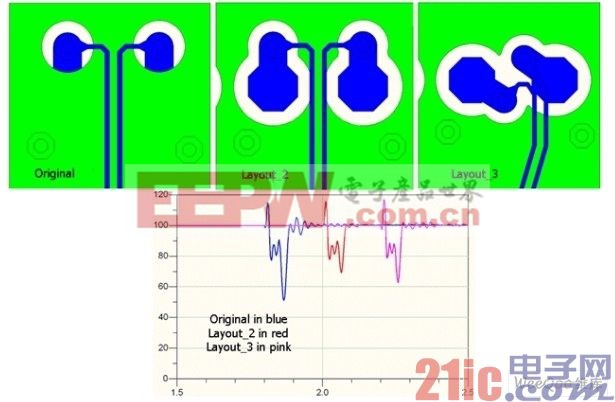

圖3顯示了原來布局的變化(在焊點/通孔區)及其對差分TDR性能的影響。這些略大于焊點的孔是在焊點上的金屬層Layout_2上實現的。原有布局的電容dip現在大約小到20Ω。另一個來自Layout_2的試圖修改的部分是從松散耦合到緊耦合來改變通孔定位,如Layout_3所示。緊耦合通孔旨在提高差分對的串擾性能。它已在另一項研究中得到證明,串擾性能的改善微乎其微,這里不介紹這項研究的其他內容。Layout_3的粉色波形顯示,由于額外兩個通孔之間的電容耦合,電容dip略差。

圖3 三種布局的差分TDR響應

回波損耗性能的影響

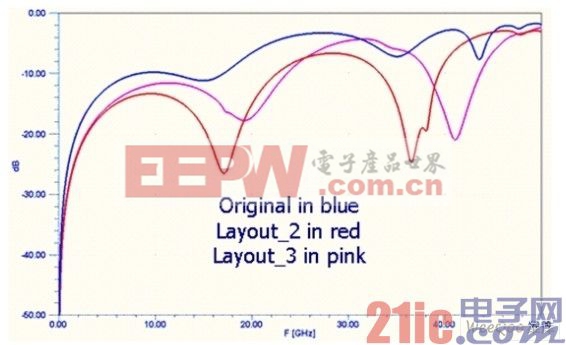

圖4顯示了每次修改后回波損耗性能的影響。Layout_3原始布局的整體回波損耗最差。Layout_2 顯示出最佳的整體回波損耗,它直接關系到其TDR性能。

在5GHz下Layout_2的回波損耗為-16dB,而在10GHz下為-14dB,可以輕易滿足基頻為-15dB的規范,以及10Gbps SerDes接口一次諧波頻率-10dB的規范。

圖4 每次修改后回波損耗性能的影響

片芯焊點環布局的影響

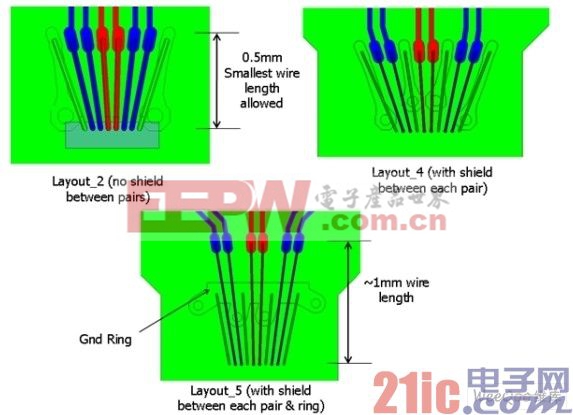

為了盡量減少對間串擾,理想的是用回波焊點隔開芯片上的每個差分對。當邊緣速率在20-30ps級時,由于干擾源-受擾者串擾,可能嚴重惡化接收器性能,這一點至關重要。要保持通孔和焊球焊點區與Layout_2一致,圖5給出了與芯片封裝鍵合線連接相關的兩個額外的封裝布局變化。

圖5 片芯焊點環和鍵合線布局變化

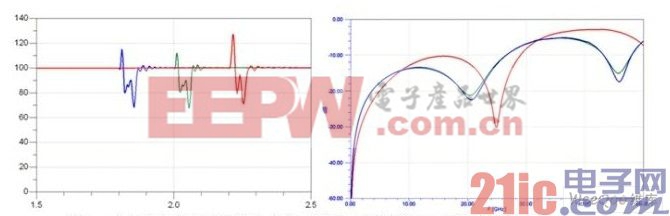

圖6顯示了三個布局的差分TDR和回波損耗性能。藍色的Layout_2響應與前邊的圖一樣。由于相對較小的間斷電感,但其頻域影響不變,Layout_4的TDR性能稍好。Layout_5 TDR響應顯示,由于相對于其他兩個布局的鍵合線,感應尖峰幾乎為2倍。圖6也顯示了長鍵合線對回波損耗性能惡化的直接影響。

圖6 由于片芯焊點環和鍵合線布局的改變影響了TDR和回波損耗性能

本文小結

本文解釋了鍵合線封裝中的兩個主要不連續區;討論了10Gbps數據速率范圍優化鍵合線封裝布局的快速技術;也顯示了鍵合線長度對回波損耗性能惡化的影響。

評論