基于多IP核復用SoC芯片的可靠性研究

IP核間通信總線的穩定性直接關系到整個系統的可靠性。我們對IP核間的通信進行了研究, 加入一些檢錯模塊, 保證通信時數據的正確性, 進而提高整個系統的可靠性。

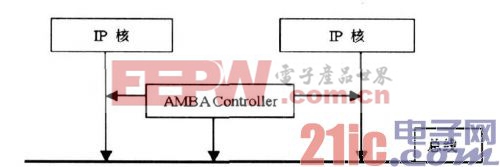

圖4

IP核間通信采用AMBA 2. 0 AHB 和APB 片上總線協議, 增加一個AMBA Controller模塊對整個AMBA 片上通信進行監控,通過檢錯信號反饋信息對該模塊采取進一步的保護措施, 當出錯時, 使整個流水線重啟, 保證通信數據正確, 錯誤數據被拋棄。檢錯算法采用2位奇偶校驗。

IP核間可靠性通信原理如圖4所示。

2. 3 嵌入BIST電路, 檢測IP核的工作狀態

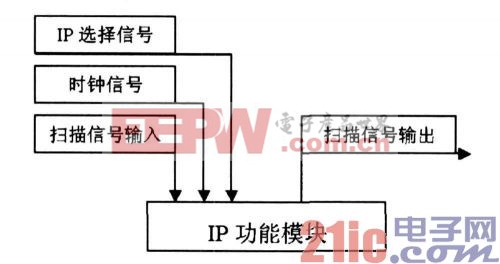

B IST ( Built- In SelfTest) 是一種芯片內建自測試, 即在芯片上集成一種自我檢測的電路。基于DFT思想, 在片上集成了一種B IST模塊來提高系統的可靠性。在芯片內增加產生激勵和做測試分析的電路, 使芯片不但能完成邏輯功能, 還能在外部給定測試方式命令時進行自我測試分析, 并輸出結果。這種結構的電路既不需要準備測試碼, 也不需要專門的測試設備。電路中包含有測試碼生成部件、掃描測試電路和測試結果輸出部件, 如圖5 所示。

圖5

SoC 芯片在上電運行中自動對自己的運行狀態進行監控, 并通過掃描輸出信號即時返回該IP功能模塊的狀態信息, 在其它控制模塊中再根據這些狀態信息采取相應策略保證SoC 的可靠運行。

3 結束語

對于SoC 芯片, 可靠性是首要考慮的問題, 基于多IP復用SoC 的設計技術, 重點解決處理器的可靠性、多IP核間通信的可靠性、IP核工作異常狀態研究, 可以進一步提高SoC 芯片的可靠性。

近幾年來本單位根據智能終端產品特點, 進行智能終端專用SoC 芯片研發, 在SoC的設計過程中充分考慮了其可靠性, 加入了非常全面的可靠性算法, 采用奇偶校驗、TMR(三模冗余)寄存器、片上EDAC、流水線重啟和強迫CACHE 不命中等多層次容錯機制來提高SoC的可靠性, 已在FPGA 驗證平臺上得到驗證, 并進行SoC 芯片流片和批量生產驗證, SoC 芯片的可靠性得到大幅度提高, 驗證本方法可行, 具有很好的推廣價值。

評論