一種電子系統(tǒng)認(rèn)證芯片的電源規(guī)劃

摘要:為了對所開發(fā)的電子產(chǎn)品進(jìn)行保護(hù),采用ASIC的方法設(shè)計基于硬加密技術(shù)的電子系統(tǒng)認(rèn)證芯片。在后端物理設(shè)計中,為了使最終的芯片實現(xiàn)面積優(yōu)化且滿足功耗、時序等要求,采用預(yù)設(shè)計的方法對芯片進(jìn)行功耗預(yù)估與布線擁塞分析。根據(jù)分析結(jié)果提高了芯片利用率,并針對預(yù)設(shè)計中存在的電壓降(IR Drop)違規(guī)進(jìn)行了詳細(xì)的電源規(guī)劃,包括全局電源網(wǎng)絡(luò)的連接、電源環(huán)和電源條的設(shè)計,最終滿足了功耗要求,實現(xiàn)了時序收斂以及面積優(yōu)化。

關(guān)鍵詞:系統(tǒng)認(rèn)證;電源規(guī)劃;功耗分析;電壓降

0 引言

為了防止所研發(fā)的電子產(chǎn)品被非法克隆,一種有效的方法是采用硬加密技術(shù)對電子產(chǎn)品進(jìn)行保護(hù)。硬加密技術(shù)是指依賴特定的硬件實現(xiàn)系統(tǒng)保護(hù),主機(jī)需要訪問相應(yīng)的硬件進(jìn)行認(rèn)證后才能正常工作,具有抗解密強(qiáng)度高,穩(wěn)定性和兼容性好等優(yōu)點(diǎn)。

本文所研究的電子系統(tǒng)認(rèn)證芯片是基于硬加密技術(shù)采用專用集成電路(ASIC)設(shè)計的方法來實現(xiàn)的。由于ASIC上有特殊算法,PCB和一些硬件可能被復(fù)制,但是無法復(fù)制ASIC的加密數(shù)據(jù),保密性更強(qiáng)。該芯片采用RSA加密算法,它是非對稱密鑰密碼體制的代表,其安全性在于找到兩個大素數(shù)p和q比較容易;但目前沒有有效的方法從p和q的乘積N中分解出p和q。有專家建議,普通公司使用1 024位的密鑰就可以保證資料的安全性,因此該系統(tǒng)認(rèn)證芯片采用密鑰為1 024位的RSA加密算法。

該電子系統(tǒng)認(rèn)證芯片采用SMIC 0.18μm 6層金屬工藝,在SoC Eneounter平臺上進(jìn)行物理設(shè)計。為了了解整個芯片的布線擁塞程度和功耗的大概情況,進(jìn)行正式設(shè)計之前,對該芯片進(jìn)行預(yù)設(shè)計;通過預(yù)設(shè)計的結(jié)果分析芯片的布線擁塞情況,并對布局布線后的功耗進(jìn)行預(yù)估。在分析預(yù)設(shè)計的基礎(chǔ)上,針對預(yù)設(shè)計中存在的問題對芯片進(jìn)行詳細(xì)的電源規(guī)劃,為整個芯片設(shè)計出一個合理的供電網(wǎng)絡(luò),使最終的設(shè)計實現(xiàn)面積優(yōu)化,并且滿足功耗、時序等要求。

1 功耗預(yù)估

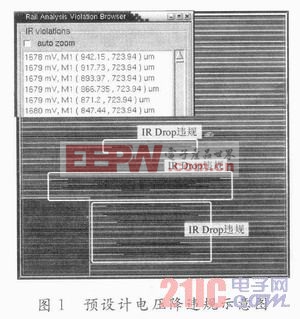

預(yù)設(shè)計采用75%的利用率,對該電子系統(tǒng)認(rèn)證芯片進(jìn)行了粗略的布圖規(guī)劃,僅設(shè)計了寬度為10 μm的電源環(huán)。為了使芯片功耗的分析結(jié)果更接近實際,對該芯片進(jìn)行了布局、時鐘樹綜合和詳細(xì)布線等步驟。在時序收斂的前提下,進(jìn)行功耗分析,工作電壓VDD為1.8 V,得到芯片的總功耗為115.41 mW,包括開關(guān)功耗(Switehing Power)、內(nèi)部功耗(Internal Power)和泄露功耗(Leakage Power)。但是芯片中存在IRDrop違規(guī)(即芯片中的電壓降超過了5%VDD),如圖1所示,左上角的對話框中列出了存在IR Drop違規(guī)的地方,具體位置在版圖中的深色區(qū)域。一般情況下,5%的電壓降會增大10%~15%的線延遲,會產(chǎn)生時序違規(guī),使芯片處于不正常的工作狀態(tài),因此,需要在后續(xù)設(shè)計中進(jìn)行詳細(xì)的電源規(guī)劃。

采用75%的利用率進(jìn)行詳細(xì)布線后發(fā)現(xiàn),版圖中的布線擁塞情況并不嚴(yán)重,Meta15和Meta16的布線資源均比較寬裕。一些研究表明,芯片成本與芯片面積的4次方成正比。為了降低成本,應(yīng)盡可能減小芯片面積。經(jīng)過反復(fù)嘗試之后,確定芯片的利用率為80%,芯片內(nèi)核(Core)面積約為2.474 mm2,總面積約為3.5 mm2,比預(yù)設(shè)計時減小了約0.12 mm2。

2 電源規(guī)劃

在該電子系統(tǒng)認(rèn)證芯片的預(yù)設(shè)計階段,存在IRDrop的違規(guī),因此必須通過電源規(guī)劃來設(shè)計芯片的供電網(wǎng)絡(luò),以消除IR Drop違規(guī)。電源規(guī)劃的總體步驟包括全局電源網(wǎng)絡(luò)的連接、電源/地Pad規(guī)劃、電源環(huán)的設(shè)計和電源條的設(shè)計。

評論