基于PI控制的全數字鎖相環設計

摘要:針對以往全數字鎖相環研究中所存在電路結構復雜、設計難度較大和系統性能欠佳等問題,提出了一種實現全數字鎖相環的新方法。該鎖相環以數字比例積分控制的設計結構取代了傳統的一些數字環路濾波控制方法。應用EDA技術完成系統設計,并進行計算機仿真。仿真結果表明:在一定的頻率范圍內,該鎖相環鎖定時間最長小于15個輸入信號周期,相位抖動小于輸出信號周期的5%,且具有電路結構簡單、環路性能好和易于集成的特點。

關鍵詞:比列積分控制;全數字鎖相環;超高速集成電路硬件描述語言;現場可編程門陣列

鎖相環在通信、無線電電子學和自動控制等領域得到了極為廣泛的應用,它已成為各類電子系統中一個十分重要的部件。由于全數字鎖相環(ADPLL)消除了模擬鎖相環中壓控振蕩器(VCO)的非線性,鑒相器不精確,部件易飽和以及高階環不穩定等特點,而其本身又具有參數穩定、可靠性高、易于集成的特點,因此,ADPLL得到了越來越多的應用。傳統的數字鎖相環系統是希望通過采用具有低通特性的環路濾波器,獲得穩定的振蕩控制數據。對于數字濾波器采用基于DSP的運算電路的全數字鎖相環,當環路帶寬很窄時,環路濾波器的實現將需要很大的電路量,這給專用集成電路的應用和片上系統SoC(System on Chip)的設計帶來一定困難。另一種類型的全數字鎖相環是采用脈沖序列低通濾波計數電路作為環路濾波器,如隨機徘徊序列濾波器、先N后M序列濾波器等。這些電路通過對鑒相器模塊產生的相位誤差脈沖進行計數運算,獲得可控振蕩器模塊的振蕩控制參數。由于脈沖序列低通濾波計數方法是一個比較復雜的非線性處理過程,難以進行線性近似。因此,無法采用系統傳遞函數的分析方法確定鎖相環的設計參數,不能實現對全數字鎖相環性能指標的解耦控制和分析,無法滿足較高的應用要求。

針對上述全數字鎖相環存在的問題,本文提出了采用具有比例積分特性的數字控制方法來實現環路濾波的全數字鎖相環。整個系統采用VHDL語言編程設計,使用QuartusⅡ軟件對系統設計進行編譯和仿真驗證,給出了計算機的仿真結果。

1 全數字鎖相環的結構及工作原理

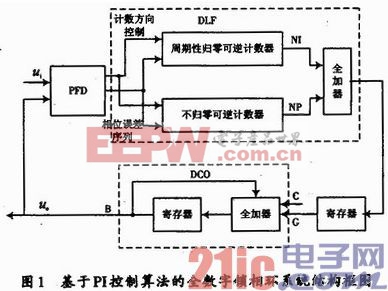

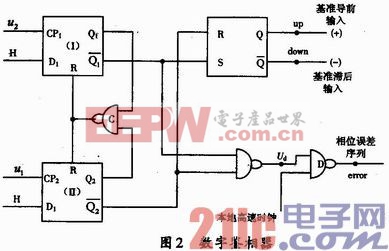

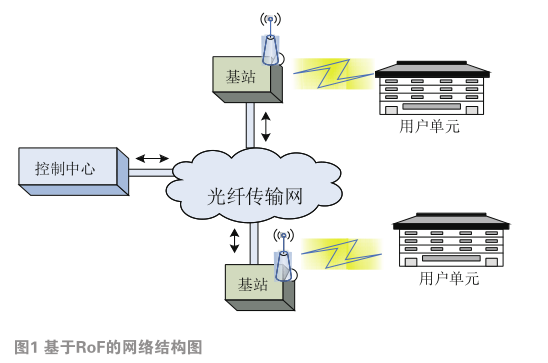

基于比例積分控制算法的二階全數字鎖相環的系統結構,如圖1所示。該系統由數字鑒相器(Phase Frequency Detector,PFD)、數字環路濾波器(Digital LoopFilter,DLF)和數控振蕩器(Digitally Controlled Oseillator,DCO)三個部分組成。數字鑒相器由雙D觸發器、RS鎖存器和與非門構成,電路原理圖如圖2所示。此數字鑒相器具有鑒頻功能和鑒相功能,其線性鑒相范圍是±2π。當兩個輸入信號的頻率相等時,其輸出為兩輸入信號之間的相位差;當兩個輸入信號的頻率不等時,其輸出為兩輸入信號之間的頻率差。因此,在數字鎖相環路中使用這種鑒相器,對頻率捕捉是非常有利的。在環路鎖定之前,鑒相器起鑒頻器的作用,使DCO的頻率向輸入信號頻率靠近。環路鎖定之后,鑒相器的輸出正比于兩輸入信號之間的相位差,保持環路鎖定。

數字環路濾波器的主要作用是抑制噪聲及高頻分量,并且控制環路相位校正的速度與精度。其工作原理是對鑒相器輸出的相位誤差經一階積分環節和比列環節調節后,分別產生積分控制參數NP和比例控制參數NI,然后取出這兩個控制參數之和作為數控振蕩器的控制參數。為了使DLP輸出的控制碼組在同一瞬間并行送入DCO,在這兩個環路部件之間接入一緩沖寄存器。數字鑒相器送來的頻率/相位誤差序列分別作為周期性歸零可逆計數器和不歸零可逆計數器的時鐘輸入端。周期性歸零可逆計數器是每周期計數值輸出的同時被清零一次,不歸零可逆計數器是一直計數而不被清零。兩個可逆計器的計數方向控制信號是由數字鑒相器送來本地估算信號導前或滯后于輸入信號的標志信號。不歸零可逆計數器相當于一個理想積分環節,而周期性歸零的可逆計數器相當于比例環節。數控振蕩器由全加器和寄存器構成的累加器組成。若累加器位長為N,則低位輸入端NL接DLF的控制碼組G,高位NH接DCO自由振蕩頻率f0的控制碼組C(該參數可由設計者設定)。當控制碼組G均為‘0’時,DCO輸出端最高位AN的輸出信號的頻率便是DCO的自由振蕩頻率f0。在環路鎖定過程中,控制碼組G不是全為零,此時累加器的累加結果將進位而改變累加器的分頻系數,從而改變DCO輸出信號的頻率,實現比例積分控制參數對本地估算信號的控制作用,最終達到鎖定的目的。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

塵埃粒子計數器相關文章:塵埃粒子計數器原理 鑒相器相關文章:鑒相器原理 數字濾波器相關文章:數字濾波器原理 鎖相環相關文章:鎖相環原理 鎖相放大器相關文章:鎖相放大器原理

評論