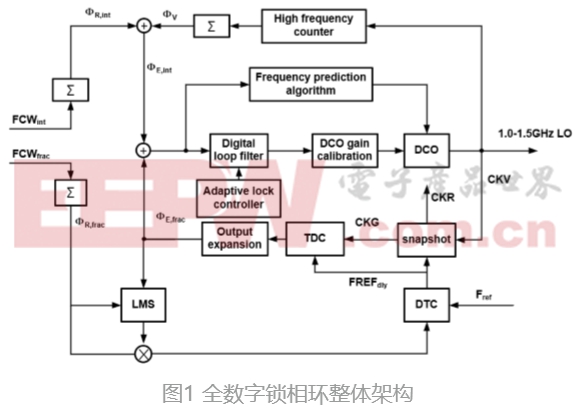

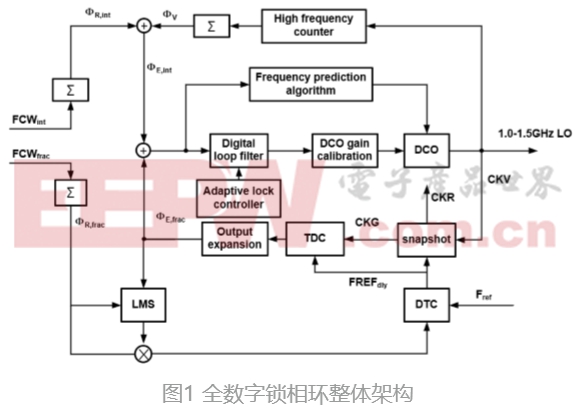

- 譚寧禹 (大連理工大學?微電子學院,遼寧?大連?116024)摘? 要:近年來,5G和物聯網應用對片上系統時鐘提出了新的需求。鎖相環在片內發揮著重要的作用,以產 生不同的時鐘源。這些新需求的主要關注點快速鎖定、低功耗、低噪聲和小面積。隨著CMOS工藝的發展,模 擬鎖相環的工作電壓逐漸降低,其設計面臨著巨大的挑戰。根據市場需求,采用全數字鎖相環(ADPLL)進行數 字設計,以減少設計時間和設計工作量。此外,使用標準單元實現的ADPLL不僅可以加快設計時間,而且可以 提高可移植性。當系統處于休眠狀態時,鎖相環

- 關鍵字:

202003 全數字鎖相環 快速鎖定 頻率預測算法

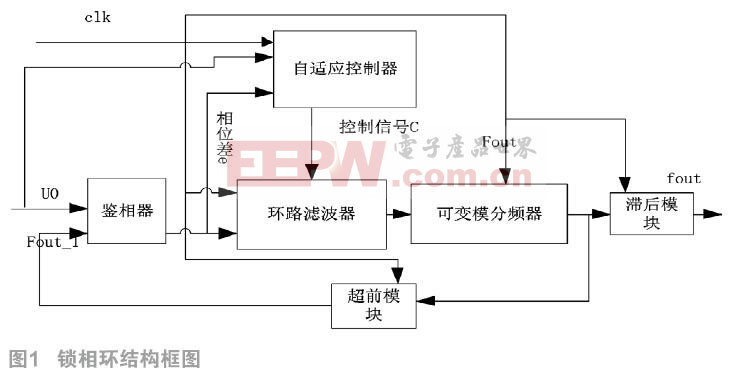

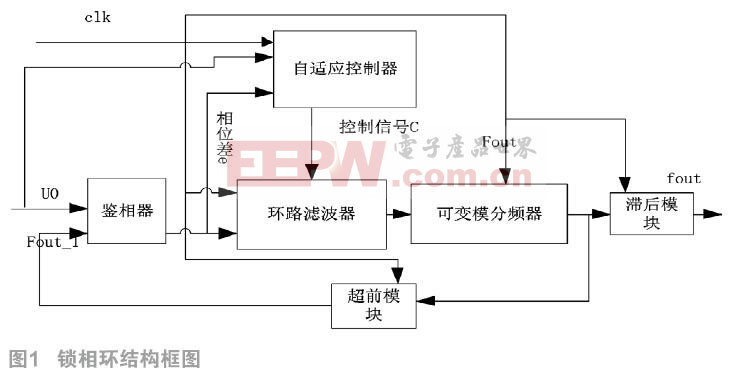

- 針對無線電能傳輸頻率跟蹤設計中傳統鎖相環電路設計復雜、跟蹤速度慢、鎖相頻帶窄和無超前滯后環節,單獨模塊設計修改繁瑣等問題,對自變模全數字鎖相環進行改進, 與傳統的全數字鎖相環相比,該鎖相環采用可變模分頻器,使得中心頻率可變,鎖相范圍增大;通過前饋回路進行鑒頻調頻,提高了鎖相速度;同時,其環路濾波器采用比例積分結構,使得鎖相輸出無靜差且比例積分參數依據相位差自動進行調節;通過參數設置可調節輸出信號的相位。應用modelsim進行仿真,并進行實物驗證證實了該設計具有寬范圍的鎖相能力及快速精確的頻率跟蹤性能。

- 關鍵字:

全數字鎖相環 比例積分控制 FPGA 無線電能傳輸 201706

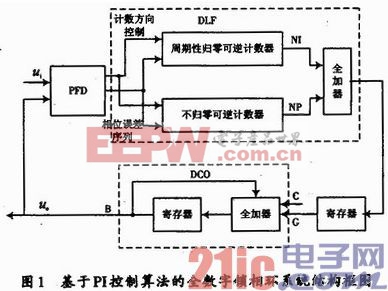

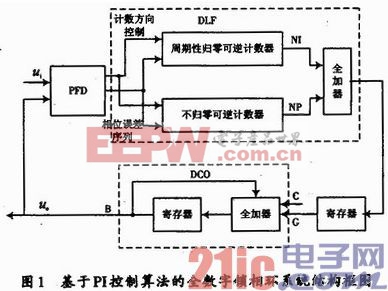

- 針對以往全數字鎖相環研究中所存在電路結構復雜、設計難度較大和系統性能欠佳等問題,提出了一種實現全數字鎖相環的新方法。該鎖相環以數字比例積分控制的設計結構取代了傳統的一些數字環路濾波控制方法。應用EDA技術完成系統設計,并進行計算機仿真。仿真結果表明:在一定的頻率范圍內,該鎖相環鎖定時間最長小于15個輸入信號周期,相位抖動小于輸出信號周期的5%,且具有電路結構簡單、環路性能好和易于集成的特點。

- 關鍵字:

比列積分控制 全數字鎖相環 超高速集成電路硬件描述語言 現場可編程門陣列

- 摘要:本文在說明全數字鎖相環的基礎上,提出了一種利用FPGA設計一階全數字鎖相環的方法,并給出了關鍵部件的RTL可綜合代碼,并結合本設計的一些仿真波形詳細描述了數字鎖相環的工作過程,最后對一些有關的問題進行了討論。關鍵詞:全數字鎖相環;DPLL;FSK;FPGA 引言鎖相環(PLL)技術在眾多領域得到了廣泛的應用。如信號處理,調制解調,時鐘同步,倍頻,頻率綜合等都應用到了鎖相環技術。傳統的鎖相環由模擬電路實現,而全數字鎖相環(DPLL)與傳統的模擬電路實現的PLL相比,具有精度高且不受溫度和電壓影響,環路

- 關鍵字:

DPLL FPGA FSK 全數字鎖相環

全數字鎖相環介紹

您好,目前還沒有人創建詞條全數字鎖相環!

歡迎您創建該詞條,闡述對全數字鎖相環的理解,并與今后在此搜索全數字鎖相環的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473