基于FPGA的F-RAM防掉電設(shè)計(jì)

摘要 在復(fù)雜實(shí)驗(yàn)條件下,需采用非易失性鐵電存儲器記錄重要數(shù)據(jù)。為防止二次上電時(shí)實(shí)驗(yàn)數(shù)據(jù)被覆蓋,需設(shè)計(jì)防掉電功能。文中介紹了一種F-RAM的防棹電設(shè)計(jì)思路,并基于現(xiàn)場可編程門陣列實(shí)現(xiàn),板級驗(yàn)證工作正常,并已在相關(guān)項(xiàng)目中得到應(yīng)用且達(dá)到了預(yù)期功能。

本文引用地址:http://www.104case.com/article/201610/308466.htm關(guān)鍵詞 非易失鐵電存儲器;防掉電;現(xiàn)場可編程門陣列

在彈載、密閉艙等某些復(fù)雜實(shí)驗(yàn)條件下,為記錄實(shí)驗(yàn)數(shù)據(jù),國內(nèi)外通常采用SRAM加后備電池、EEPROM、NVRAM的3種方式。其中SRAM加后備電池的方法增加了硬件的復(fù)雜性,同時(shí)又降低了系統(tǒng)的可靠性;EEPROM的寫操作時(shí)間較長;NVRAM的價(jià)格限制了其的普及應(yīng)用。鑒于以上情況,越來越多的設(shè)計(jì)者將注意力投向了新型的非易失性鐵電存儲器(F-RAM)。非易失性鐵電存儲器具有實(shí)時(shí)寫入,讀寫操作簡單,可擦寫次數(shù)可達(dá)億次量級,并具有低功耗等突出優(yōu)點(diǎn)。

系統(tǒng)實(shí)驗(yàn)中可能會出現(xiàn)二次上電情況,此時(shí)系統(tǒng)再次正常工作,將向F-RAM中重新寫入數(shù)據(jù),造成已采集有效數(shù)據(jù)的覆蓋,為避免數(shù)據(jù)覆蓋的發(fā)生設(shè)計(jì)中需增加防掉電功能。本文主要介紹一款F-RAM芯片的硬件配置、讀寫操作時(shí)序,闡明了防掉電設(shè)計(jì)思路及其FPGA實(shí)現(xiàn),同時(shí)驗(yàn)證了方法的正確性。

1 F-RAM及FPGA

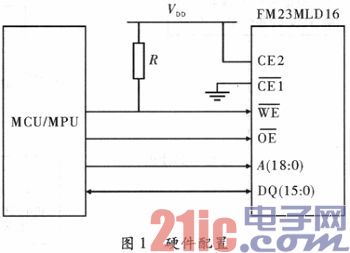

本文選擇FM23MLD16的8 Mbit F-RAM存儲器,48個(gè)管腳BGA封裝,可抗高過載,作為FPGA的外設(shè)器件。首先器件配置應(yīng)正確,硬件配置決定了軟件的控制及時(shí)序。根據(jù)手冊,本文選擇如圖1所示的配置方式。

硬件上

接為低電平、CE2接為高電平,程序中將UB、LB接成低電平以配置成數(shù)據(jù)位寬16bit模式。根據(jù)硬件配置,讀寫操作利用

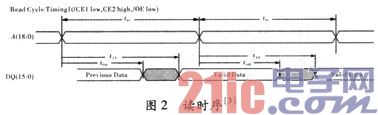

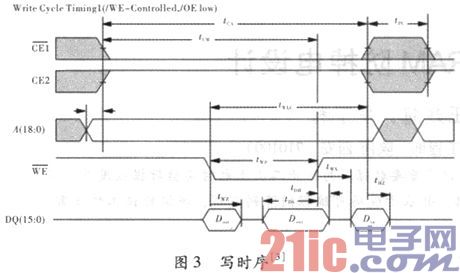

、

兩信號控制,且時(shí)序關(guān)系確定,如圖2和圖3所示。硬件配置中需注意的是

上拉電阻務(wù)必要加入,以保證在上電及掉電時(shí)

信號不為低電平。

設(shè)計(jì)需滿足時(shí)序要求,對F-RAM的讀寫時(shí)鐘最終確定為5 MHz。由圖2可知該配置下,讀操作相對簡單,

為低,

為高,地址變化即可;寫操作需注意

的上升沿與地址、數(shù)據(jù)間滿足建立時(shí)間、保持時(shí)間要求,文中

的上升沿處于數(shù)據(jù)中段。

FPGA既具有門陣列的高邏輯密度和高可靠性,又具有用戶可編程特性,可減少系統(tǒng)設(shè)計(jì)和維護(hù)的風(fēng)險(xiǎn),降低產(chǎn)品成本,并縮短設(shè)計(jì)周期。FPGA有著規(guī)整的內(nèi)部邏輯塊陣列和豐富的連線資源,適合于細(xì)粒度和高并行度結(jié)構(gòu)特點(diǎn)的數(shù)字信號處理任務(wù),可大幅提高系統(tǒng)處理速度。管腳資源豐富是采用FPGA實(shí)現(xiàn)的重要原因,且時(shí)序控制方便。

2 防掉電設(shè)計(jì)思路

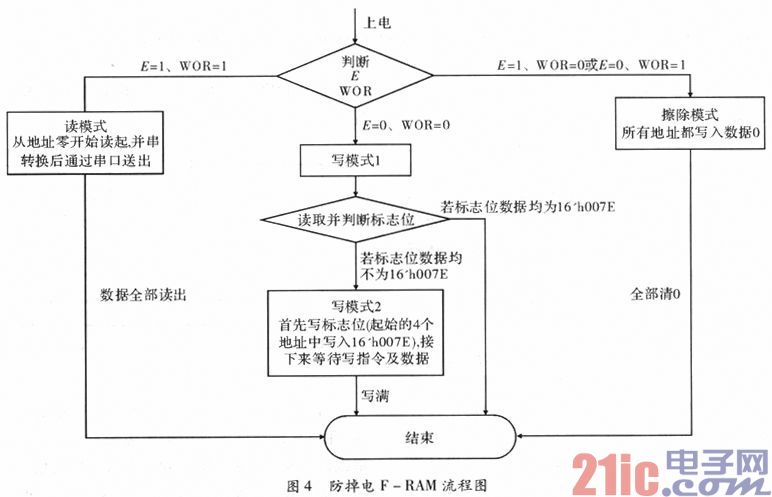

正常的讀寫操作,在所選擇硬件配置下滿足時(shí)序要求即可。防掉電功能通過在寫模式上電后,首先以判斷標(biāo)志位的方式實(shí)現(xiàn),若標(biāo)志位未寫入標(biāo)志信息,則執(zhí)行寫操作,否則進(jìn)入空閑模式不再寫入。而讀模式將存儲器內(nèi)數(shù)據(jù)正常讀出即可。設(shè)計(jì)增加擦除模式,將F-RAM中所有數(shù)據(jù)清零,且標(biāo)志位也清零。

讀寫及擦除模式間的切換是通過兩外置管腳的輸入電平來控制的,兩管腳可實(shí)現(xiàn)4種組合滿足本文的需要,上電時(shí)通過判斷管腳電平進(jìn)入相應(yīng)模式。其設(shè)計(jì)流程如圖4所示。

圖4中E、WOR為兩個(gè)外置的控制管腳,0、1代表高低電平。為數(shù)據(jù)分析方便,設(shè)計(jì)每包數(shù)據(jù)均加幀頭、幀尾標(biāo)志信息。最初的設(shè)計(jì)思路為在標(biāo)志位寫固定值,上電寫操作模式下先讀取該標(biāo)志位,擦除也只是將標(biāo)志位清零。后經(jīng)分析可將幀頭作為標(biāo)志信息,這樣大幅簡化了設(shè)計(jì)復(fù)雜度。每包數(shù)據(jù)幀頭均由4個(gè)16'h007E構(gòu)成,將其作為標(biāo)志位,則寫模式下,判斷初始4個(gè)地址中是否為該標(biāo)志位即可判別是否已寫入數(shù)據(jù),實(shí)現(xiàn)防掉電功能。擦除模式下將所有存儲數(shù)據(jù)均清為0。每次上電后系統(tǒng)重新判斷E、WOR狀態(tài),而讀寫地址均從0開始重新變化。

3 板級驗(yàn)證

由于該器件為FPGA外置芯片,因此讀寫操作的正確性需在信號處理板上進(jìn)行調(diào)試,設(shè)計(jì)中的仿真只保證讀寫時(shí)序與設(shè)計(jì)思路一致。

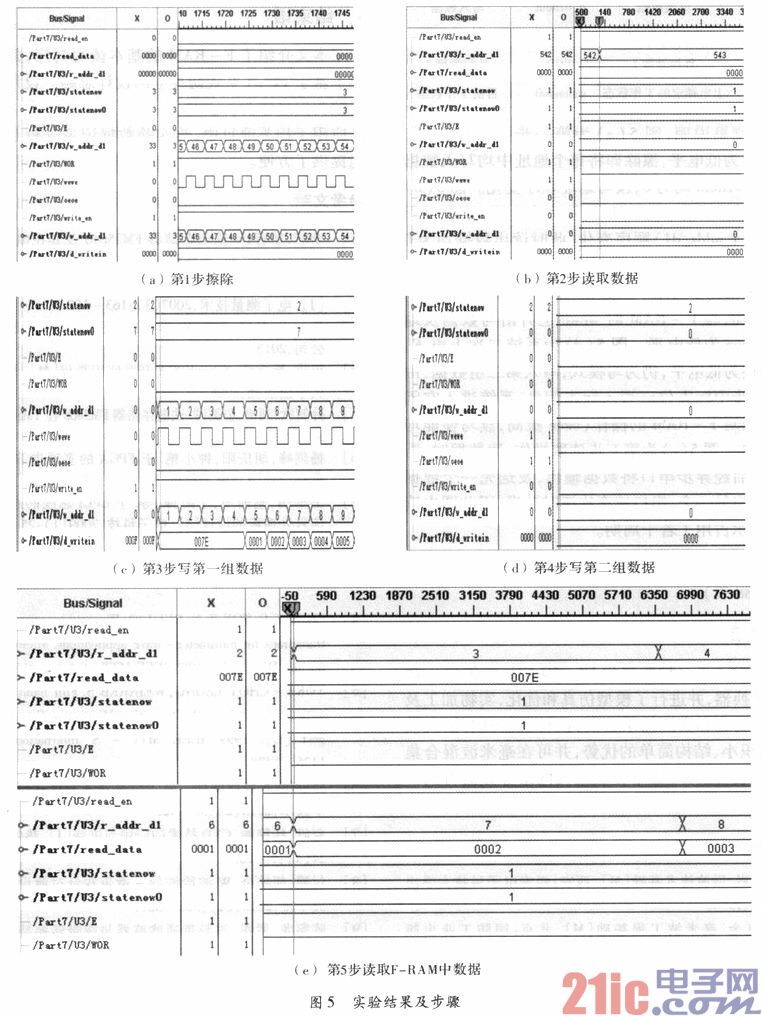

板級驗(yàn)證方法:實(shí)驗(yàn)前控制E、WOR為擦除模式,數(shù)據(jù)清空。再接為寫模式,則可正常寫入數(shù)據(jù),重新上電,仍處于寫模式,此時(shí)標(biāo)志位已寫入標(biāo)志信息,則結(jié)束進(jìn)入空模式而不再重新寫入,最后再進(jìn)入讀模式。具體步驟為:(1)進(jìn)行擦除操作,然后系統(tǒng)掉電。(2)讀操作看是否將F-RAM中數(shù)據(jù)清為0,然后系統(tǒng)掉電。(3)寫操作重復(fù)寫入同一組已知格式的數(shù)據(jù)(16 bit位寬),本文采用:4個(gè)幀頭(16'h007E)+數(shù)據(jù)(16'd 1、2、…、800)+2個(gè)幀尾作為第一組數(shù)據(jù),寫滿后系統(tǒng)掉電。(4)二次寫操作,仍保持E、WOR為低電平,此時(shí)每幀數(shù)據(jù)封裝格式不變,將數(shù)據(jù)調(diào)整為800,799,…,1,然后系統(tǒng)掉電。(5)讀操作,從F-RAM中讀取數(shù)據(jù),若為第一組數(shù)據(jù)則結(jié)果正確。實(shí)驗(yàn)結(jié)果如圖5(a)~圖5(c)所示,分別對應(yīng)(1)~(5)步實(shí)驗(yàn)步驟。

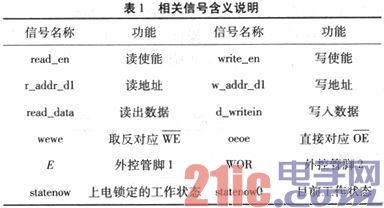

圖5為使用同一bit文件觀測,圖中相關(guān)信號的說明如表1所示。

實(shí)驗(yàn)結(jié)果說明,圖5(a)為第一步擦除操作,E、WOR均接為低電子,擦除即將每個(gè)地址中均寫入數(shù)據(jù)0,對應(yīng)d_writein均為0,按寫地址順序變化。圖5(b)為第二步讀取操作,E、WOR均接為高電平,讀取過程中讀地址(r_addr_d1)順序變化,此時(shí)讀出數(shù)據(jù)均為0(read_data),說明第一步擦除有效已將標(biāo)志位清零。圖5(c)為第三步寫第一組數(shù)據(jù),如圖所示寫地址隨數(shù)據(jù)順序增加,寫F-RAM時(shí)wewe上升沿與數(shù)據(jù)及地址對齊,oeoe為低電平。圖5(d)為系統(tǒng)二次上電E、WOR均接為低電平,仍為寫模式,寫入第二組數(shù)據(jù),由于在第三步中標(biāo)志位已寫入標(biāo)志信息,系統(tǒng)進(jìn)入空閑模式,結(jié)束對F-RAM的操作(oeoe拉高,讀寫使能均為低電平)。圖5(c)為第五步讀取操作,讀數(shù)據(jù)時(shí),需并串轉(zhuǎn)換后經(jīng)異步串口將數(shù)據(jù)輸出,發(fā)送完一個(gè)數(shù)據(jù)后將再讀出另一個(gè),串口速率比讀時(shí)鐘慢,因此圖中讀一個(gè)數(shù)顯示占用了若干周期。

圖5(c)的結(jié)果說明讀出數(shù)據(jù)為實(shí)驗(yàn)第三步即第一次寫入的數(shù)據(jù),重復(fù)驗(yàn)證結(jié)果不變,說明達(dá)到了防掉電的目的,且讀寫功能正常,符合設(shè)計(jì)要求。

設(shè)計(jì)中考慮試驗(yàn)時(shí)可能遇到的E、WOR線斷情況,故給兩控制管腳均接入下拉電阻,避免了控制寫操作時(shí)E、WOR變?yōu)楦唠娖剑M(jìn)而防止了誤操作的發(fā)生。

4 結(jié)束語

本文介紹了F-RAM的基本讀寫時(shí)序,并著重說明了基于FPGA實(shí)現(xiàn)防掉電的設(shè)計(jì)思路。設(shè)計(jì)利用數(shù)據(jù)幀頭信息作為標(biāo)志位,簡化了邏輯復(fù)雜度。該方法已應(yīng)用于相關(guān)項(xiàng)目中,為實(shí)驗(yàn)數(shù)據(jù)記錄分析及查找問題提供了方便。

評論