一種基于頻率預測算法的快速鎖定全數字鎖相環

譚寧禹 (大連理工大學?微電子學院,遼寧?大連?116024)

摘? 要:近年來,5G和物聯網應用對片上系統時鐘提出了新的需求。鎖相環在片內發揮著重要的作用,以產 生不同的時鐘源。這些新需求的主要關注點快速鎖定、低功耗、低噪聲和小面積。隨著CMOS工藝的發展,模 擬鎖相環的工作電壓逐漸降低,其設計面臨著巨大的挑戰。根據市場需求,采用全數字鎖相環(ADPLL)進行數 字設計,以減少設計時間和設計工作量。此外,使用標準單元實現的ADPLL不僅可以加快設計時間,而且可以 提高可移植性。當系統處于休眠狀態時,鎖相環功耗控制著系統的待機功耗。因此,如果鎖相環可以快速鎖定 頻率和相位,鎖相時間就可以減少,這樣鎖相環就可以在低功率模式下關閉。本文提出了一種基于頻率預測算 法的快速鎖定ADPLL。該鎖相環在中芯國際 130 nm CMOS工藝中進行了實現和驗證。

0 引言

近年來,隨著5G和物聯網的發展,鎖相環(PLL)在 片上系統(SoC)中扮演著重要的角色。在一個SoC中, 通常需要幾個鎖相環為不同的I/O接口提供不同的時鐘 源。鎖相環產生不同的頻率,適用于不同的應用場合, 廣泛應用于移動通信系統、無線通信系統和生物醫學電 子領域。傳統鎖相環是由電荷泵鎖相環實現的,在先進 的CMOS工藝中,鎖相環的設計面臨泄漏電流的挑戰。 此外,電壓控制振蕩器(Kvco)的增益由于控制電壓范圍 的縮小而增大。因此,它很容易遭受噪聲對控制電壓的 影響。傳統鎖相環中含有一些無源器件,模擬環路濾波 器芯片面積大、成本高。并且傳統鎖相環鎖相時間長, 功耗高。因此,隨著工藝尺度的減小,由VCO、電荷泵 和模擬環路濾波器組成的鎖相環不適合新的要求,即低 功耗、低電壓、低芯片面積,尤其是快速鎖定。

全數字鎖相環(ADPLL)利用了CMOS工藝的優 點[1],與傳統鎖相環相比,ADPLL采用數字電路代替無 源器件。將VCO轉換為數字控制振蕩器(DCO),并將模 擬濾波器轉換為數字濾波器。芯片尺寸減小,芯片成本 相應降低。因此,ADPLL可以在低電壓下工作,芯片 面積小。

為了實現快速鎖定,需要對全數字鎖相環引入快速 鎖定算法。這里采用了一種新穎的頻率預測算法來對數 控振蕩器控制字進行預測,來加快鎖定速度。

1 快速鎖定全數字鎖相環

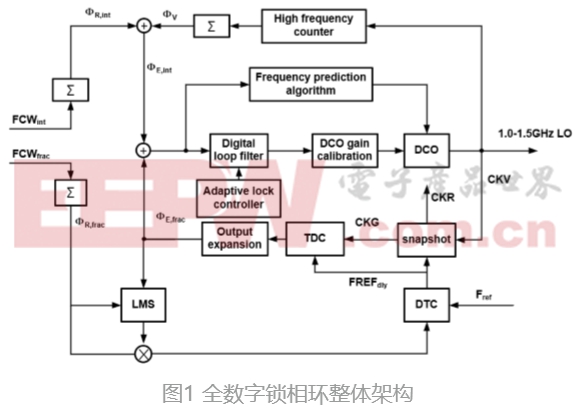

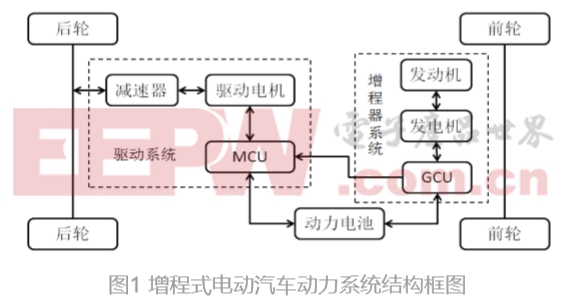

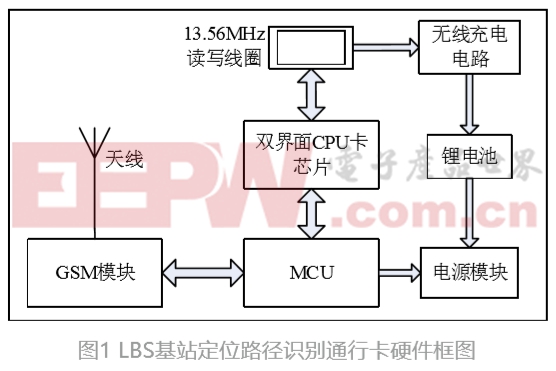

1.1 全數字鎖相環架構 采用基于計數器的全數字鎖相環系統結構[2],本論 文提出了一種寬頻帶的,低功耗的、能夠實現自適應快 速鎖定的全數字鎖相環系統架構,如圖1所示。其中,模擬電路包括數字時間轉換器、時間數字轉換器、LC 數控振蕩器。高速數字電路包含有snapshot電路、可變 時鐘相位累加器、Σ-Δ調制器。而低速數字電路則包含 有限狀態機、數字濾波器、相位檢測器、DTC增益校正 電路、TDC輸出擴展電路、DCO增益校正電路、DCO 細調bank行列控制邏輯、DTC輸入溫度碼解碼電路[3]。

首先,整數輸入分頻比和輸出時鐘分別累加得到整 數相位與可變相位。之后,這兩個相位被送到相位檢測 器中進行做差,得到整數相位差。同時,參考時鐘通過 數字時間轉換器進行延遲,得到。采用一個快照電路提 供重定時時鐘CKR和門控時鐘CKG,利用時間數字轉換 器檢測CKG和之間的分數相位差。隨后,整體的相位差 通過將和 相加得到。最后,一個數字濾波器將處理得 到數控振蕩器控制字來控制數控振蕩器的振蕩頻率。

1.2 頻率預測算法

快速鎖定算法在原理上包含兩種類型。第一個是在 環路開始運行之前預測數控振蕩器控制字。該方法減 小了初始相位差。另一種是采用換檔算法自適應控制 帶寬。既滿足鎖定速度的要求,又滿足相位噪聲的要 求[4]。

由于我們為了獲得較好的相位噪聲,選擇了LC振 蕩器,而不是環形振蕩器,LC振蕩器的調諧曲線并不 是嚴格線性的,所以與環形振蕩器相比其頻率預測無法 直接精確得到控制字的值,但是由于粗調和中調陣列的 調諧步長較大,所以仍然可以得到較為精確的預測值。

在鎖定過程中,DCO輸出周期可以看做是粗調控制字和中調控制字的函數,對于采用線性度極高的由相同 的延時單元級聯組成的環形振蕩器來說,該函數關系可 以看成是嚴格線性的,所以,直接采用基于線性關系的 頻率估計算法進行一次線性插值即可以實現快速鎖定。 但是對于LC振蕩器,輸出頻率 ,一方面受限于工藝庫,片上電感的值在整個輸出頻率范圍內會有 1 nH左右的波動,另一方面,電容值隨著控制字是線性 變化的,所以輸出頻率f隨著控制字的變化是斜率遞增 的,輸出周期隨著控制字的變化是斜率遞減的,因此輸 出周期與控制字并不是嚴格線性的。為了在覆蓋較大的 頻率調諧范圍的同時,實現較為精細的頻率分辨率, DCO的調諧陣列采用了三級調節的方式,粗調陣列調諧 步長26 MHz/LSB,中調陣列2.5 MHz/LSB,細調陣列 60 kHz/LSB,其中粗調和中調陣列采用了type I環路控 制,相對于傳統的type II環路可以加快鎖定速度,而細 調陣列采用type II環路控制,有利于壓制相位噪聲,實 現最終的鎖定。所以,可以針對粗調控制字利用線性插 值法進行頻率預測,進一步加快鎖定速度。

,一方面受限于工藝庫,片上電感的值在整個輸出頻率范圍內會有 1 nH左右的波動,另一方面,電容值隨著控制字是線性 變化的,所以輸出頻率f隨著控制字的變化是斜率遞增 的,輸出周期隨著控制字的變化是斜率遞減的,因此輸 出周期與控制字并不是嚴格線性的。為了在覆蓋較大的 頻率調諧范圍的同時,實現較為精細的頻率分辨率, DCO的調諧陣列采用了三級調節的方式,粗調陣列調諧 步長26 MHz/LSB,中調陣列2.5 MHz/LSB,細調陣列 60 kHz/LSB,其中粗調和中調陣列采用了type I環路控 制,相對于傳統的type II環路可以加快鎖定速度,而細 調陣列采用type II環路控制,有利于壓制相位噪聲,實 現最終的鎖定。所以,可以針對粗調控制字利用線性插 值法進行頻率預測,進一步加快鎖定速度。

線性插值的原理如下,輸入時鐘周期Pref 和輸出時 鐘周期Pckv的比例R是粗調控制字和中調控制字的函數:

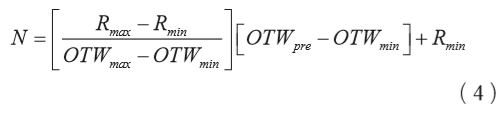

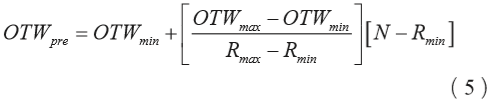

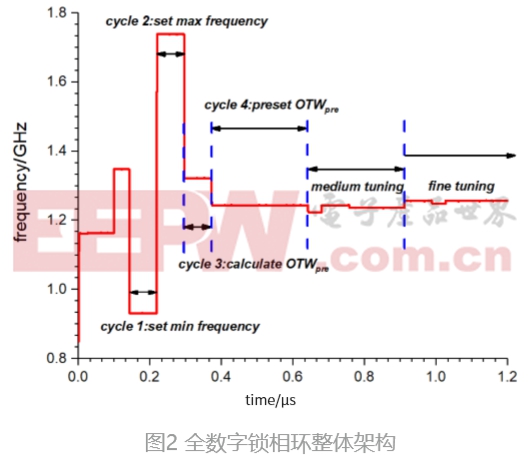

針對實際中的LC振蕩器,R隨著粗調控制字和中調 控制字的增加而減小,但并不是嚴格的線性變化,可以 采用線性插值進行擬合。目標是找到使得周期比最接 近理想整數分頻比FCW時的粗調諧字[5]。在系統重置之 后,有限狀態機首先控制系統進入頻率預測狀態。整個 頻率預測過程需要四個時鐘周期來完成,如圖2所示。

第1個周期設置控制字OTWmax=31,控制DCO震蕩 在最高頻率,通過計數器測得此時的R的最大值:

第2個周期設置控制字OTWmin=0,控制DCO震蕩在 最低頻率,通過計數器測得此時的R的最小值:

第3個周期利用線性插值法,設定線性插值的區間 為(R min,Rmax),根據線性插值公式:

得到線性插值預測值:

第4個周期利用該線性插值預測值對粗調陣列進行 預置數,可以縮小初始狀態的相位差,縮短鎖定時間。

2 仿真結果

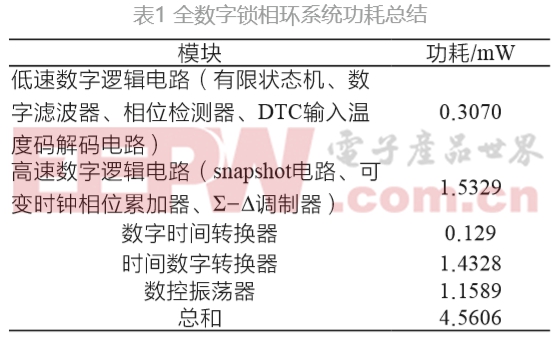

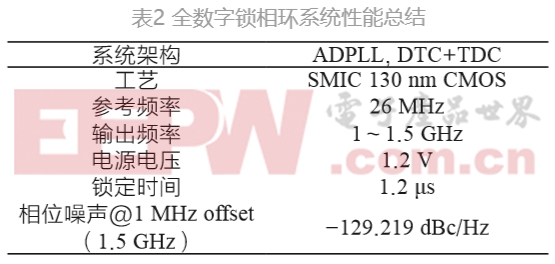

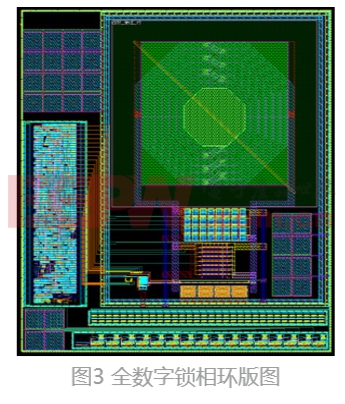

本ADPLL在中芯國際130 nm CMOS工藝中實現。 系統功耗總結如下表1。系統性能總結如表2所示。系統 版圖如圖3所示。

3 總結

本文提出了一種新的快速鎖定全數字鎖相環,該 ADPLL具有功耗低、面積小、噪聲低、鎖相速度快等 優點。引入的頻率預測算法可以在環路鎖定開始前完成 數控振蕩器控制字的預測,從而極大減小上電和跳頻時 的鎖定時間,滿足快速鎖定的需求。

參考文獻:

[1] LIU Y H, HEUVEL VAN DEN J H C, KURAMOCHI T, et al. An Ultra-Low Power 1.7-2.7 GHz Fractional-N SubSampling Digital Frequency Synthesizer and Modulator for IoT Applications in 40 nm CMOS[J]. IEEE Transactions on Circuits and Systems, 2017, 64(5): 1094–1105.

[2] LIU H, TANG D, SUN Z, et al. A Sub-MW Fractional-N ADPLL With FOM of -246 dB for IoT Applications[J]. IEEE Journal of Solid-State Circuits, 2018, 53(12): 3540–3552.

[3] 應用于射頻無線通信系統的多模分數分頻頻率綜合器的設計和 研究[D]. 上海:復旦大學, 2012.

[4] CHUNG C C, LO C K. A Fast Lock-in All-Digital PhaseLocked Loop in 40-nm CMOS Technology[J]. IEICE Electronics Express, 2016, 13(17): 20160749.

[5] CHEN Y W, HONG H C. A Fast-Locking All-Digital Phase Locked Loop in 90nm CMOS for Gigascale Systems[J]. 2014 IEEE International Symposium On Circuits and Systems (ISCAS), 2014: 1134–1137.

本文來源于科技期刊《電子產品世界》2020年第03期第73頁,歡迎您寫論文時引用,并注明出處。

評論