基于FPGA的PCI Express應用平臺設計

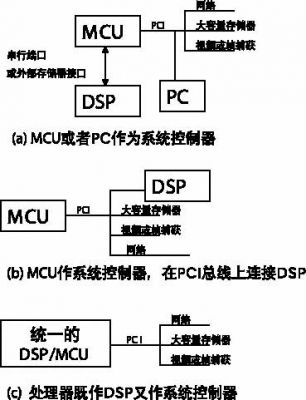

傳統的數據傳輸應用平臺是基于PCI總線設計實現的。PCI總線是并行共享總線,具有數據傳輸速率慢等缺點。隨著點對點高速串行PCI Express(Peripheral Component Int erconnect Express,PCI—E)總線的發展,基于PCI—E總線的新型數據傳輸應用平臺已逐漸取代了傳統的基于PCI總線數據傳輸應用平臺。PCI-E總線不僅在系統軟件級與PCI總線兼容,且與PCI等傳統總線相比具有更高的帶寬和靈活的可配置通道數。

本文引用地址:http://www.104case.com/article/201610/308362.htm以FPGA為核心設計數據傳輸應用平臺,具有硬件電路設計簡單、可重構性、提供片上PCI—E IP硬核、并可實現SOPC功能等特點。所以在計算機、通信等領域獲得了廣泛應用,更使得高速系統設計不必過多地關注PCI—E總線的復雜設計,大幅提高了設計的可靠性,縮短了設計的研發周期。本文設計實現了基于FPGA的PCI Express應用平臺。

1 方案實施基礎

1.1 PCI-E協議規范

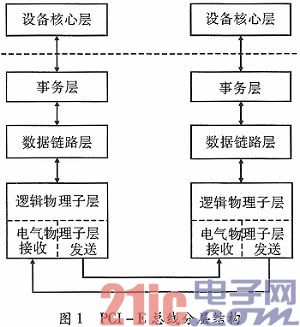

PCI—E作為第三代I/O技術由Intel公布,并隨后被PCI—SIG (Peripheral Component Interconne—ct Special Interest Group)正式命名為“PCI Expres—s。作為串行連接方式的總線,PCI—E協議規范定義了一種分層的設備體系結構,包括事務層(Transaction Layer)、數據鏈路層(Data Link Layer)和物理層(PhysicalLayer),所有數據的接收和發送過程中均以包的形式在各層之間傳輸。PCI—E總線的層次結構如圖1所示。

(1)事務層是PCI—E中的最上層,負責事務層包(Transaction Layer Packet,TLP)的封裝與分解,并進行流速控制管理、數據包隊列管理以及利用多虛擬通道提供服務質量(Quality of Service)。

(2)數據鏈路層是PCI—E的中間層,主要負責完成數據完整性檢查、錯誤檢測與糾正。數據鏈路層實現了包的應答和重傳機制,每個包用一個唯一的標識來確保應答可正確地定位請求,若出錯則重傳出錯標識的所有后續包,以此保證數據的可靠性。

(3)物理層分為邏輯物理子層和電氣物理子層。邏輯物理子層完成與數據鏈路層的數據交換、8b/10b編解碼、并串和串并轉換。電氣物理子層負責對每路串行數據進行差分驅動傳輸。

(4)設備核心層并不屬于PCI—E協議規范。其主要向事務層提供封裝TLP所需的數據,或接收事務層拆包后的數據。

1.2 FPGA器件選型

選用Altera公司的Cyclone IV GX系列FPGA為核心實現PCI—E數據傳輸應用平臺。該系列FPGA器件包含多達8個3.125 Gbit·s-1速率的全雙工高速收發器,并支持物理編碼子層(PCS)、物理介質附加子層(PMA)和PCI—E IP硬核,可完全實現PCI—E基本規范所需的2.5 Gbit·s-1速率、8b/10b編解碼和PCI—E分層協議棧,并可減少應用平臺設計的難度,且加快了研發周期。

2 應用平臺設計

基于PCI—E總線設計了一種Windows XP操作系統下的數據傳輸及處理應用平臺,滿足PCI—E基本規范所需的總線傳輸速率和分層體系結構,并可通過多種數據傳輸模式來適用于不同的應用場合,如數據采集、數據下發和數據處理等。應用平臺設計包括軟件和硬件兩部分組成,硬件部分包括FPGA內部邏輯電路,PCI—E IP硬核等;軟件部分包括上位機控制程序和應用平臺在Windows操作系統下的驅動程序。

2.1 硬件設計

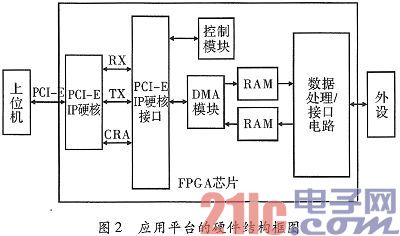

硬件設計主要包括PCI—E IP硬核接口、控制模塊、DMA模塊和數據處理/接口電路,應用平臺的硬件結構如圖2所示。

(1)PCI—E IP硬核接口完成PCI—E IP硬核與設備核心層之間的數據橋接功能。PCI—E IP硬核實現了PCI—E的協議規范,還提供了與設備核心層的接口。Cyclone IV GX系列器件提供的PCI—E IP硬核與設備核心層的接口為一組內存映射(Avalon Memory Map)接口,其中包括TX接口、RX接口和CRA接口。

TX接口是指由設備核心層發起的數據傳輸接口,映射了事務層存儲器的讀和寫請求事務。TX接口支持突發數據傳輸,實現設備核心層與PCI—E硬核接口的高速數據傳輸。

RX接口是指由上位機發起的數據傳輸接口,是對事務層存儲器讀和寫事務的映射。用作上位機發送控制命令的接口。

CRA接口是PCI—E IP硬核配置空間訪問接口,通過此接口可訪問PCI—E IP硬核的配置寄存器,并完成對PCI—E IP硬核的初始化和配置。此接口可由設備核心層直接訪問或上位機通過RX接口訪問。

(2)控制模塊主要完成設備核心層數據傳輸和數據處理控制。上位機通過RX接口向控制寄存器寫入命令字,控制模塊則通過解析命令字,啟動相應的模塊完成命令。根據應用的不同,控制模塊可由CPU或電路實現。CPU可通過編寫不同的應用軟件來完成相對復雜的控制,但運行速率有限。雖然電路的運行速率較高,但復雜的控制命令將使電路的設計變得復雜。

(3)DMA模塊實現上位機與應用平臺之間高速數據傳輸。該模塊包含兩個獨立的DMA通道,通道1控制數據從上位機到應用平臺的數據下發傳輸;通道2控制數據從應用平臺到上位機的數據上傳。上位機通過RX接口控制應用平臺上的DMA模塊實現數據下發和上傳操作。應用平臺上包含下發和上傳緩存,分別緩存來自上位機的下發數據和來自外設輸入的上傳數據。每個緩存均由兩塊獨立的8 kB RAM組成,兩塊8 kB RAM采用乒乓工作方式,實現不間斷的高速數據傳輸。

(4)數據處王里/接口電路是PCI—E設備的功能模塊,實現PCI—E應用平臺的數據處理或接口電路功能,如數據采集中實現采集設備的接口電路,或在圖像處理中完成對圖像信號的處理算法等。

2.2 傳輸模式一

適用于高速數據上傳,這種模式主要是將外設采集到的數據通過PCI—E總線數據傳輸應用平臺高速上傳至上位機。其工作流程如下:

(1)將平臺配置為上傳模式。

(2)由上位機通過RX接口向控制模塊寫入數據上傳命令,而控制模塊在接到命令后啟動外設開始采集數據,外設將采集的數據通過數據處理/接口電路送入FPGA內部兩塊8 kB的緩存RAM中。

(3)控制模塊同時啟動DMA模塊,將FPGA內部兩塊8 kB RAM緩存的輸入數據采用乒乓工作方式上傳到上位機。

(4)當DMA數據傳輸完成時,通過RX接口通知上位機數據傳輸完成,上位機采用查詢方式進行數據提取等項操作,至此一次傳輸任務完成。

2.3 傳輸模式二

傳輸模式二適用于高速數據下發,這種模式主要是將上位機數據通過PCI—E總線數據傳輸應用平臺高速下發至外設。其工作流程如下:

(1)將平臺配置為下發模式。

(2)由上位機通過RX接口向控制模塊寫入數據下發命令,控制模塊在接到命令后啟動DMA模塊從上位機中讀出數據,并寫入到8 kB RAM中。

(3)同時數據處理/接口電路采用乒乓工作方式從8 kB RAM中讀出數據,并輸出到外設。

(4)當DMA數據傳輸完成時,通過RX接口通知上位機數據傳輸完成,上位機采用查詢方式獲取DMA數據傳輸狀態,至此一次傳輸任務完成。

2.4 傳輸模式三

傳輸模式三適用于高速數據上傳或下發,這種模式中PCI—E應用平臺先完成對上位機中待處理數據的下發,然后將FPGA處理后的數據再上傳到上位機。傳輸模式三可看作模式一與模式二的混合應用。其不同之處在于,模式三執行模式一操作,或執行模式二操作,不能兩種同時執行。模式三適用于高速數據靈活收發的工作方式。相對于模式一或模式二來說,模式三收發速率較低。

2.5 軟件設計

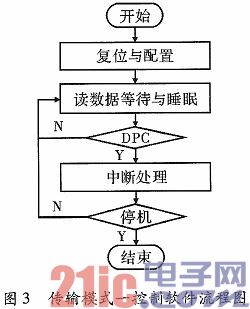

軟件設計包括應用平臺的設備驅動和不同傳輸模式下的控制軟件設計。傳輸模式一的控制軟件流程如圖3所示。

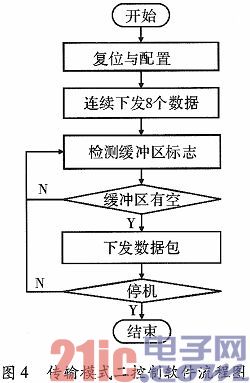

傳輸模式二的控制軟件流程如圖4所示。

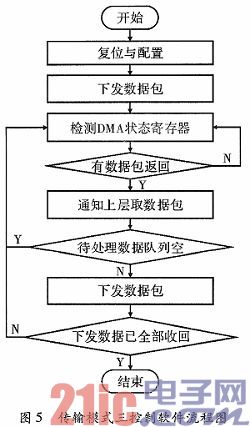

傳輸模式三的控制軟件流程如圖5所示。

設備驅動是計算機系統中軟硬件的交互接口,此應用平臺的設備驅動基于Windows下的WDF(Windows Driver Foundation)框架完成。為提高驅動效率及通用性,此設計的設備驅動將內核態的硬件資源全部映射到了應用空間,具體控制由各模式控制軟件完成。

3 驗證與實現

應用平臺采用Altera公司型號為EP4CGX50CF23C6的FPGA器件為核心,研發設計出PCI—E X4通道PCB板卡,使用Verilog HDL語言設計FPGA內部硬件電路,并在Qusrtus II 12.0開發環境下進行設計實現。基于Windows XP操作系統編寫PCI—E應用平臺驅動,進行驗證測試。受所選FPGA器件的PCI—EIP硬核限制,僅以PCI—E基礎規范1.1版本進行驗證。在傳輸模式一中,由應用平臺上的FPGA電路模擬外設生成的隨機數作為測試數據包;在傳輸模式二中,由上位機軟件產生隨機數作為測試數據包。測試數據包采用連續生成方式,生成速率>8Gbit·s-1。測試結果采用統計平均方式,即從一次連續10 s的數據傳輸量中,計算出數據的傳輸速率。

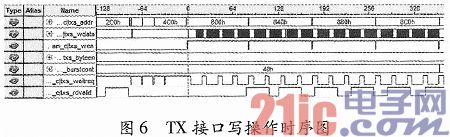

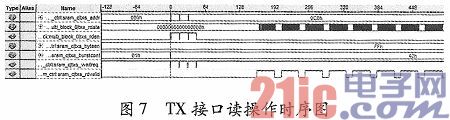

傳輸模式三下Signal Tap II邏輯分析儀捕獲的作業包長為2 kB時的TX接口寫和讀操作時序圖如圖6和圖7所示。

圖6中txs_addr表示輸出緩沖區地址,0x800表示輸出緩沖區起始地址;txs_wdata表示寫數據;txs_wen為高電平有效寫使能;txs_byteen表示字節使能;burstcont表示TX接口一次寫突發的數據長度,0x40表示此次突發長度為512字節;txs_waitreq表示TX接口等待請求,為低電平時方可進行TX接口寫操作。對于2 kB的包,TX接口需進行4次寫操作,每次寫512字節才可將FPGA內的上傳緩存RAM中的數據包寫到上位機內存中。

圖7中txs_addr表示輸入緩沖區地址,0x000表示輸入緩沖區起始地址。txs_rdvalid為高電平時txs_rdata讀數據才為有效數據。對于2 kB的包,TX接口讀操作需進行4次,每次讀512 Byte才能將上位機內存中的數據包讀到FPCA內的下發緩存RAM中。

驗證測試結果如表1~表3所示。傳輸模式一和傳輸模式二的測試速率低于PCI—E理論速率。因實際進行DMA傳輸時,需耗費一定時間,同時數據在PCI—E IP硬核傳輸過程中也不可避免的會產生一定的時間損耗,這些降低了數據的傳輸速率。傳輸模式三包括有上傳和下發兩種工作方式,此模式下上傳和下發不能同時工作,實際傳輸速率明顯降低,此外還包含傳輸模式一和二所提及的原因。

4 結束語

介紹了一種基于FPGA的PCI—E應用平臺設計,且描述了3種不同的數據傳輸模式,以Windows XP操作系統為驗證平臺,分別對3種傳輸模式進行了實現及驗證,系統工作穩定,資源利用率較高,最高傳輸速率可達7.12 Gbit·s-1。此應用平臺的設計與實現,為需要構建各種高速數據傳輸系統的設計師提供了參考。

評論