臺積電:14nm制程節點將用垂直型晶體管結構

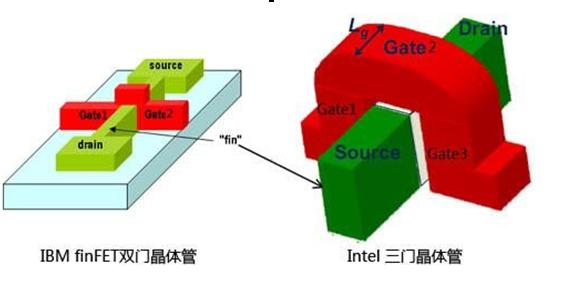

據參加了比利時微納米電子技術研究機構IMEC召開的技術論壇的消息來源透露,與會的各家半導體廠商目前已經列出了從平面型晶體管轉型為垂直型晶體管(以Intel的三柵晶體管和IBM的FinFET為代表)的計劃。

本文引用地址:http://www.104case.com/article/110130.htm其中來自半導體代工巨頭臺積電公司負責研發的高級副總裁蔣尚義在會上發言稱,臺積電公司已經決定在14nm制程節點轉向使用垂直型晶體管結構。

蔣尚義表示:“經過研究,我們決定在14nm制程節點放棄使用傳統的平面型晶體管結構,轉而采用能更好控制溝道性能的垂直型晶體管結構。”據他表示,臺積電會先從28nm制程進化到20nm制程,然后將于2015年左右的時間點直接進化到14nm制程。

與此同時,IMEC新建的1200平方米凈室車間也已經開始投入使用,這間凈室車間要比5年前初建時的面積增加了50%。這次新增的空間據稱將被用于在年底前安放由ASML公司生產的 NXT:3100 EUV極紫外光刻設備。

IMEC公司高管Thomas Hoffmann表示:“眼下向我們過問FinFET制造問題的芯片設計公司已經越來越多。”他認為由于Intel據稱會在22nm制程節點開始采用垂直型晶體管技術,加上臺積電也已經表態支持這種晶體管結構,因此引起了這些設計公司的注意,大家都想提前為這種技術做好足夠的技術準備。

“我們和我們的客戶都很想搞清楚Gate-last工藝能在FinFET晶體管中發揮出怎樣的實際性能,對那些有意在22/16nm制程轉向FinFET晶體管結構的公司來說,他們很想知道如果放棄傳統的平面型晶體管結構,那么會對現有的high-k/金屬柵極技術產生什么樣的影響。”

Intel公司率先在45nm制程節點開始啟用Gate-last工藝來制作HKMG晶體管,而臺積電也將在28nm制程節點開始啟用這種工藝。Hoffmann認為Gate-last工藝具有許多優勢,比如PMOS管的門限電壓更為穩定,而且這種工藝將原來填充在柵極區的多晶硅替換為金屬材料時,還可以為PMOS管的溝道施加一定的應變力。

不過以IBM/ GlobalFoundries/三星等Fishkill技術聯盟為代表的陣營這堅守Gate-first工藝,他們宣稱Gate-first工藝制造的晶體管密度更大,更有利于芯片核心的小型化。

在這種情況下,不少需要依賴代工廠的芯片設計公司也是舉棋不定,他們頻繁與兩方陣營往來接觸,比對雙方兩種不同HKMG制作工藝的優缺點。

Hoffmann表示:“對28nm制程低功耗芯片而言,采用gate-frist工藝已經完全可以滿足技術要求。”

評論