科研前線 | 突破DTCO瓶頸,滬兩校聯(lián)合探索GAA工藝協(xié)同優(yōu)化

直擊前線科研動(dòng)態(tài)

盡在芯片揭秘●科研前線

近日,復(fù)旦大學(xué)與華東師范大學(xué)聯(lián)合研究團(tuán)隊(duì)發(fā)表了關(guān)于DCTO協(xié)同優(yōu)化技術(shù)的研究成果,通過對(duì)于MOEL/BOEL環(huán)節(jié)的后端優(yōu)化評(píng)估方法存在的問題進(jìn)行改進(jìn),提出了新的DTCO優(yōu)化流程,并通過測(cè)試得到了最佳PPA的nanosheetFET模型。

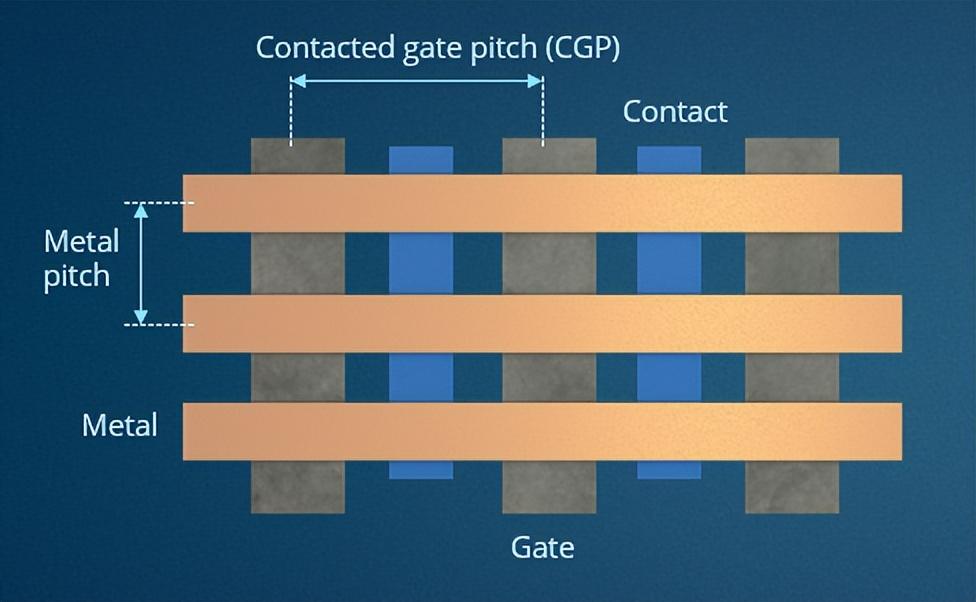

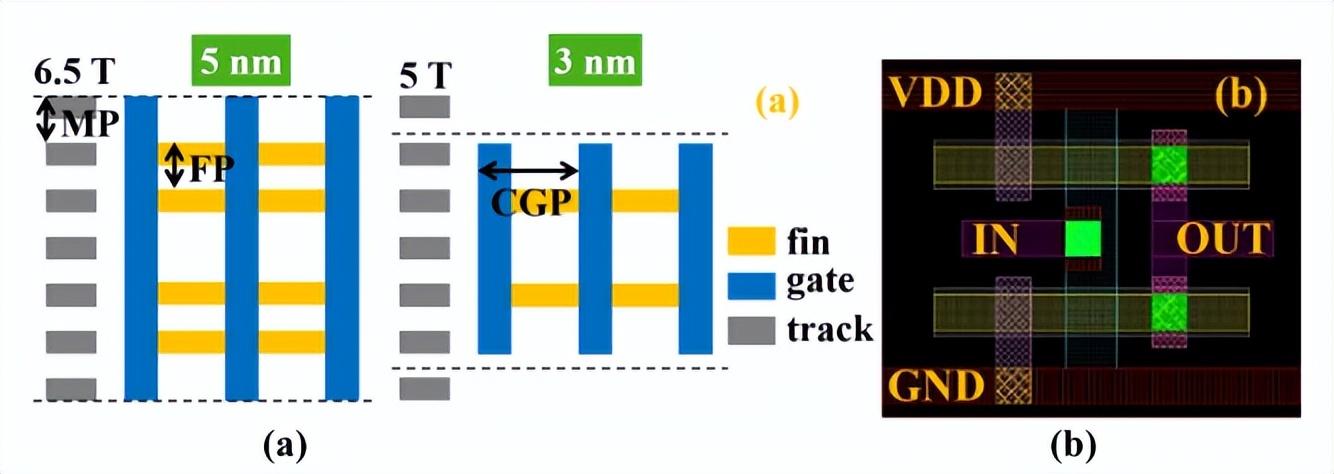

隨著集成電路晶體管特征尺寸的持續(xù)縮小,新型器件結(jié)構(gòu)也面臨著不同的性能瓶頸。以nanowire或nanosheet作為溝道形狀的GAA晶體管(以下簡(jiǎn)稱GAAFET)由于其理想的柵極靜電特性和更好的功耗-性能平衡,已被廣泛認(rèn)為是下一代集成電路制造技術(shù)核心的器件結(jié)構(gòu),目前業(yè)界正在努力推進(jìn)其研發(fā)量產(chǎn)進(jìn)程。對(duì)于基于GAAFET的邏輯電路設(shè)計(jì)而言,標(biāo)準(zhǔn)單元尺寸主要取決于CGP*和FP*兩個(gè)間距。

為降低標(biāo)準(zhǔn)單元尺寸同時(shí)滿足芯片PPA(功耗、性能與面積)設(shè)計(jì)要求,基于TCAD的DTCO得到了很大的發(fā)展,已成為先進(jìn)工藝中必不可少的環(huán)節(jié)。在DTCO中,綜合考慮工藝、晶體管結(jié)構(gòu)和電路設(shè)計(jì)目標(biāo),在優(yōu)化過程中計(jì)算和反饋電路PPA,通過技術(shù)參數(shù)的調(diào)整使工藝與電路設(shè)計(jì)相適應(yīng),實(shí)現(xiàn)最佳的電路性能。目前基于TCAD的DCTO包括FEOL工藝仿真、等效電路模型參數(shù)提取、MOEL/BOEL互連寄生參數(shù)提取、benchmark電路仿真等流程。

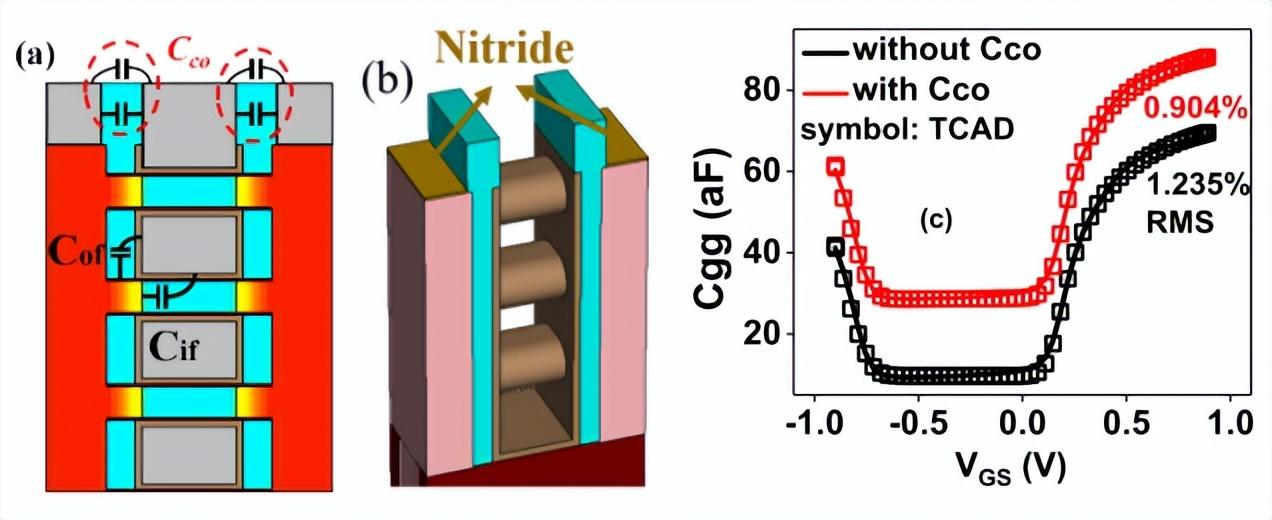

但上述估計(jì)方法存在兩個(gè)明顯的局限性:第一點(diǎn),對(duì)于任意工藝節(jié)點(diǎn),假定的等效長(zhǎng)度并不總是保持不變,尤其對(duì)于BEOL環(huán)節(jié)來說,其金屬電阻率對(duì)于工藝參數(shù)相當(dāng)敏感;第二點(diǎn),假定的等效BEOL長(zhǎng)度可能與SPX模擬提取的電容參數(shù)不匹配。在前述的DTCO流程中反復(fù)提取柵源/柵漏接觸電容Cco,也會(huì)不可避免地會(huì)影響模擬結(jié)果的準(zhǔn)確性和可信度。

為克服上述問題,復(fù)旦大學(xué)與華東師范大學(xué)聯(lián)合團(tuán)隊(duì)設(shè)改進(jìn)的BEOL和MEOL參數(shù)的評(píng)估方法,其研究成果以“Improved MEOL and BEOL Parasitic-Aware Design Technology Co-Optimization for 3 nm Gate-All-Around Nanosheet Transistor”為題發(fā)表于IEEE Transactions on Electron Devices,孫亞賓為第一作者,劉子玉為通訊作者。

*CGP,全稱contacted gate pitch,暫譯為接觸柵極間距,下圖中已標(biāo)出。

*FP,全稱fin pitch,即FinFET中相鄰Fin的距離。

圖源:Applied Materials

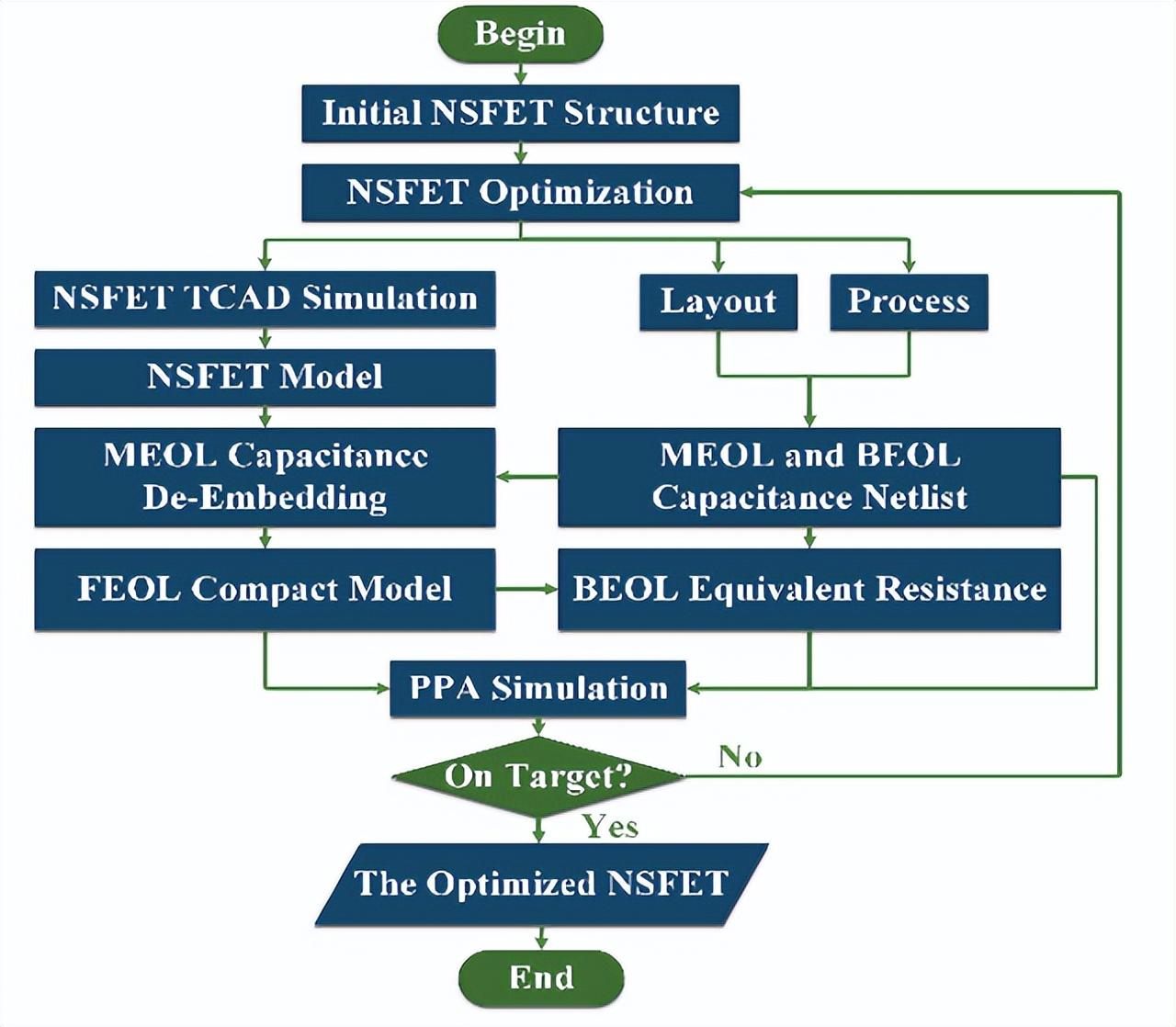

研究團(tuán)隊(duì)提出了一種改進(jìn)的DTCO流程,重新設(shè)計(jì)去嵌入方法以避免重復(fù)計(jì)算柵源/漏極接觸電容,并給出了一種用于3nmGAAFET節(jié)點(diǎn)的BEOL和MEOL電阻的評(píng)估方法。

具體工作包括:

· 基于BSIM-CMG模型對(duì)FEOL環(huán)節(jié)的電子特性進(jìn)行了描述;

· 根據(jù)版圖和工藝流程提取了互連寄生電容的netlist;

· 提取和去除了FEOL CM中重復(fù)的接觸電容和電容網(wǎng)表;

· 利用所提出的等效仿真方法,提取了BEOL等效寄生電阻;

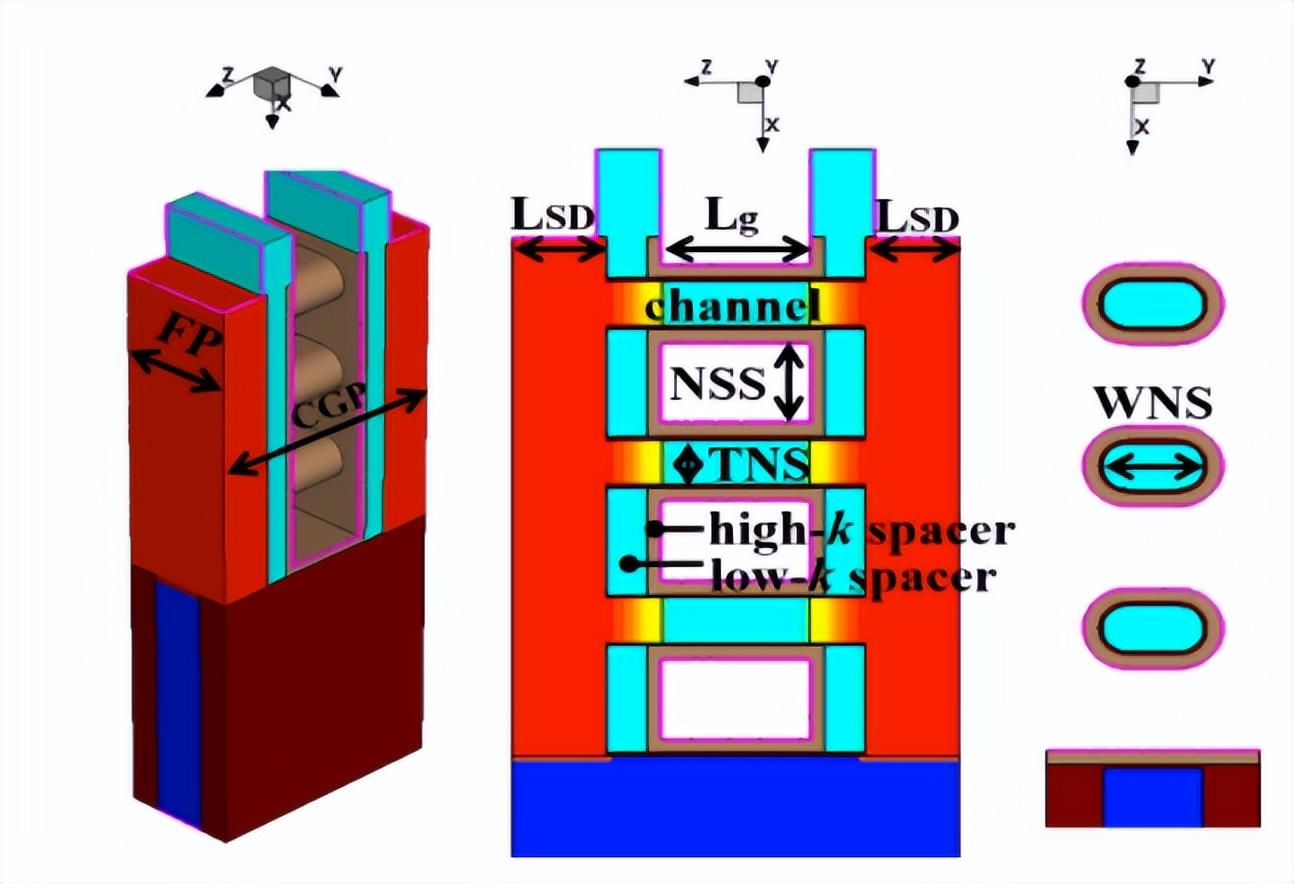

· 考慮CGP的限制和結(jié)構(gòu)對(duì)工藝的影響,通過提出的DTCO流程對(duì)nanosheetFET器件尺寸進(jìn)行權(quán)衡優(yōu)化;

· 以RO作為benchmark測(cè)試電路,得到了面積降低46%、功耗降低48%、頻率提高26%的最佳nanosheetFET模型。

本文中應(yīng)用于3nmGAAFET工藝節(jié)點(diǎn)的DCTO流程

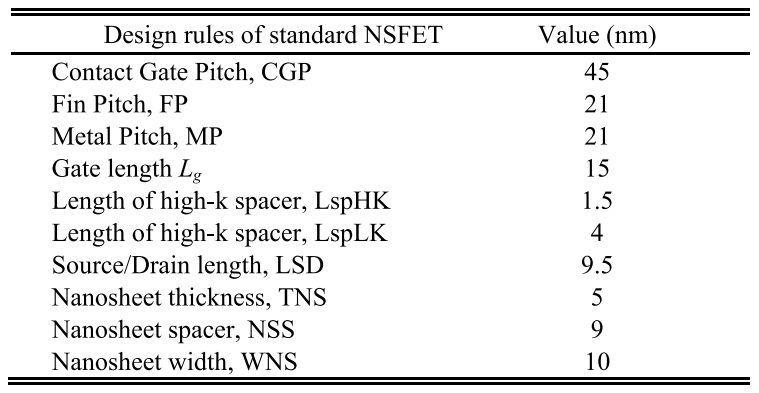

器件主要尺寸參數(shù)

器件結(jié)構(gòu)示意圖

圖(a)5/3nm標(biāo)準(zhǔn)單元版圖; 圖(b)單級(jí)反相器版圖

圖(a)nanosheetFET中寄生電容示意圖; 圖(b)寄生電容的仿真模型示意圖; 圖(c)兩種建模仿真曲線比較

本項(xiàng)研究中,復(fù)旦大學(xué)與華東師范大學(xué)聯(lián)合團(tuán)隊(duì)針對(duì)MEOL/BEOL環(huán)節(jié)的建模仿真和評(píng)估方法進(jìn)行改進(jìn)并針對(duì)多項(xiàng)關(guān)鍵參數(shù)進(jìn)行研究,得到了相對(duì)理想的GAA nanosheetFET器件結(jié)構(gòu)。這一研究發(fā)展了先進(jìn)工藝節(jié)點(diǎn)的前沿研究,為技術(shù)節(jié)點(diǎn)協(xié)同優(yōu)化技術(shù)的提供了良好的基礎(chǔ),后續(xù)系列研究也將有助于推動(dòng)GAAFET器件的設(shè)計(jì)研究與工藝發(fā)展。

*博客內(nèi)容為網(wǎng)友個(gè)人發(fā)布,僅代表博主個(gè)人觀點(diǎn),如有侵權(quán)請(qǐng)聯(lián)系工作人員刪除。