xilinx fpga 文章 最新資訊

BP神經(jīng)網(wǎng)絡(luò)圖像壓縮算法乘累加單元的FPGA設(shè)計(jì)

- 0 引 言

神經(jīng)網(wǎng)絡(luò)(Neural Networks)是人工神經(jīng)網(wǎng)絡(luò)(Ar-tificial Neural Networks)的簡稱,是當(dāng)前的研究熱點(diǎn)之一。人腦在接受視覺感官傳來的大量圖像信息后,能迅速做出反應(yīng),并能在腦海中重現(xiàn)這些圖像信息,這 - 關(guān)鍵字: FPGA BP神經(jīng)網(wǎng)絡(luò) 圖像壓縮 算法

基于AD7543和FPGA的數(shù)/模轉(zhuǎn)換電路設(shè)計(jì)

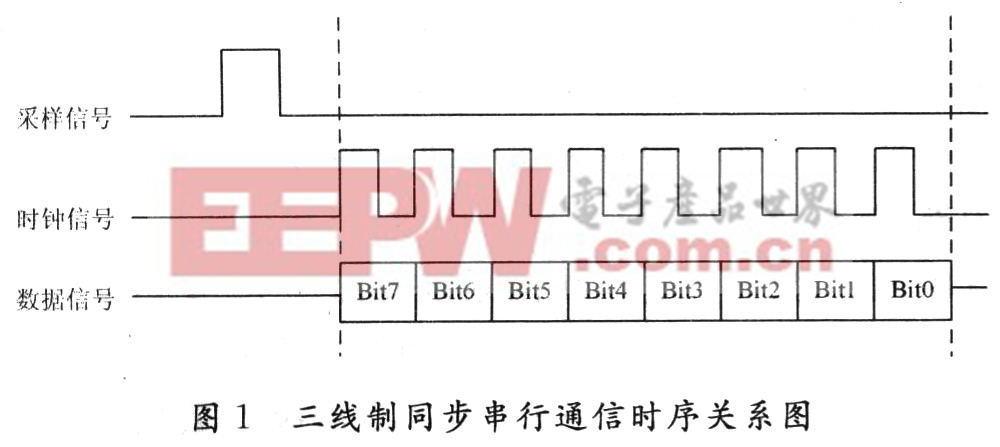

- 設(shè)計(jì)基于AD7543和FPGA的數(shù)/模轉(zhuǎn)換電路,介紹AD7543的主要特點(diǎn)、封裝形式、引腳功能和工作原理,設(shè)計(jì)基于AD7543轉(zhuǎn)換芯片的具體的數(shù)/模轉(zhuǎn)換硬件電路,利用Verilog HDL語言描述AD7543的控制時序,并給出具體的Veril-og HDL代碼及其仿真結(jié)果。實(shí)踐結(jié)果表明,該設(shè)計(jì)可行,可取代傳統(tǒng)的“CPU+專用的數(shù)/模轉(zhuǎn)換(D/A)芯片”設(shè)計(jì)結(jié)構(gòu),可進(jìn)一步提高系統(tǒng)的可靠性和抗干擾能力。

- 關(guān)鍵字: 7543 FPGA AD 模

基于FPGA玻璃缺陷圖像采集處理系統(tǒng)

- 在進(jìn)行圖像采集過程中,重點(diǎn)需要解決采集系統(tǒng)的實(shí)時性問題。而這里選用的多線陣CCD拼接圖像的采集方法勢必導(dǎo)致在低級算法階段會產(chǎn)生極大的數(shù)據(jù)流,應(yīng)用一個高速的嵌入式處理模塊則能很好地完成圖像處理的低級算法部分。在此分析了玻璃缺陷采集處理系統(tǒng)的工作過程,對系統(tǒng)內(nèi)存控制做了詳細(xì)的描述,并在FPGA內(nèi)實(shí)現(xiàn)了圖像的低級處理,從而使計(jì)算機(jī)從低級處理的大量數(shù)據(jù)中解脫出來。

- 關(guān)鍵字: FPGA 玻璃 缺陷 處理系統(tǒng)

FIR帶通濾波器的FPGA實(shí)現(xiàn)

- 為設(shè)計(jì)一個項(xiàng)目可用的FIR數(shù)字帶通濾波器,采用Matlab/Simulink軟件中DSPBulider強(qiáng)大的算法模塊設(shè)計(jì)工具,結(jié)合Altera公司的FPGA開發(fā)板實(shí)現(xiàn)FIR數(shù)字帶通濾波器的系統(tǒng)集成、RTL級仿真、綜合編譯、下載等設(shè)計(jì)流程,并對正弦信號進(jìn)行濾波,結(jié)果下載到開發(fā)板上用示波器觀測,達(dá)到了預(yù)期的濾波效果和目的。基于DSPBuilder完成系統(tǒng)建模,省去了復(fù)雜的VHDL編程,還可針對具體模塊進(jìn)行參數(shù)設(shè)置從而適應(yīng)不同的濾波需求。該方法實(shí)現(xiàn)簡單、可靠,還可類推實(shí)現(xiàn)其他復(fù)雜的嵌入式系統(tǒng)設(shè)計(jì)。

- 關(guān)鍵字: FPGA FIR 帶通濾波器

基于FPGA嵌入式的多比特自相關(guān)器設(shè)計(jì)

- 該設(shè)計(jì)利用FPGA的嵌入式軟核NiosⅡ處理器,通過嵌入式操作系統(tǒng)μC/OS-Ⅱ,實(shí)現(xiàn)了在FPGA內(nèi)的自相關(guān)計(jì)算器;利用FPGA強(qiáng)大的并行運(yùn)算功能和自帶存儲器實(shí)現(xiàn)的“乒乓”RAM,通過軟核NiosⅡ輸出控制字實(shí)時切換調(diào)用兩個“乒乓”RAM的存儲和讀取功能,使之同時完成對采集數(shù)據(jù)的緩沖存儲和向乘法器提供計(jì)算數(shù)據(jù)的功能,使芯片的整個數(shù)字處理鏈路連續(xù)化。另外,采用多比特進(jìn)行自相關(guān)運(yùn)算較之于現(xiàn)在天文臺使用的1 b量化自相關(guān)器,能有效地提高SNR退化比。

- 關(guān)鍵字: FPGA 嵌入式 比特

基于FPGA的激光無線通信精跟蹤系統(tǒng)

- 0 引 言

以大氣作為傳輸介質(zhì),激光作為信息載體進(jìn)行無線通信時,空一地激光無線通信是激光無線通信的一種常見形式,信標(biāo)光的準(zhǔn)確捕獲、瞄準(zhǔn)與跟蹤(Acquisition,Pointing and Tracking,APT)是其關(guān)鍵技術(shù),AP - 關(guān)鍵字: FPGA 激光 跟蹤系統(tǒng) 無線通信

xilinx fpga介紹

Xilinx FPGA

Xilinx FPGA主要分為兩大類,一種側(cè)重低成本應(yīng)用,容量中等,性能可以滿足一般的邏輯設(shè)計(jì)要求,如Spartan系列;還有一種側(cè)重于高性能應(yīng)用,容量大,性能能滿足各類高端應(yīng)用,如Virtex系列,用戶可以根據(jù)自己實(shí)際應(yīng)用要求進(jìn)行選擇。 在性能可以滿足的情況下,優(yōu)先選擇低成本器件。

Xilinx FPGA可編程邏輯解決方案縮短了電子設(shè)備制造商開發(fā)產(chǎn)品的時間 [ 查看詳細(xì) ]

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司