- 直接數字頻率合成技術(Direct Digital Synthesize,DDS)是繼直接頻率合成技術和鎖相式頻率合成技術之后的第三代頻率合成技術。它采用全數字技術,并從相位角度出發進行頻率合成。隨著微電子技術和數字集成電路的飛速

- 關鍵字:

Verilog HDL DDS 仿真

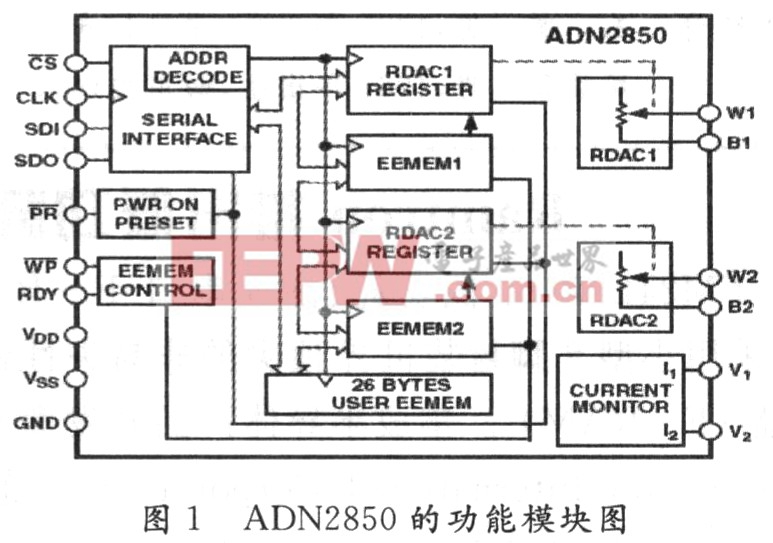

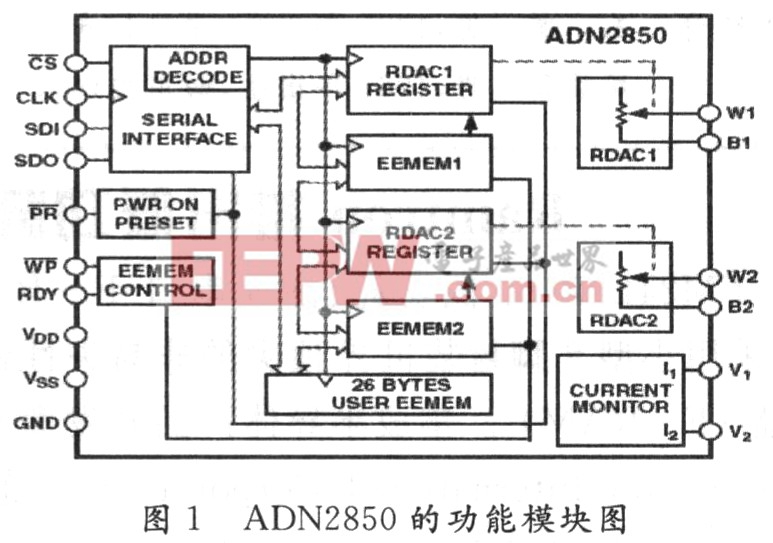

- 摘要:數字電位器由于可調精度高,更穩定,定位更準確,操作更方便,數據可長期保存和隨時刷新等優點,在某些場合具有模擬電位器不可比擬的優勢。論述對數字電位器ADN2850的一種方便的控制方法,通過計算機上的串口直

- 關鍵字:

串口 控制 ADN2850 數字電位器 Verilog HDL 基于

- 在工信部電子信息司的指導下,工業和信息化部軟件與集成電路促進中心(CSIP )聯合集成電路IP核標準工作組,現面向全國集成電路設計企業工程師、科研院所及高校師生,舉辦2009年“首屆中國開源IP核標準化設計競賽”,競賽報名工作已于6月3日啟動。報名及詳情咨詢可登錄競賽官方網站 http://www.ipmall.org.cn了解。據悉本次競賽獲獎者可分別獲得現金1萬元、5千元等獎勵,針對學生參賽者有機會獲得到IBM中國芯片設計中心實習的機會!

參賽者可以個人或團隊(不高于

- 關鍵字:

CSIP VHDL Verilog

- 0 引 言

除法器是電子技術領域的基礎模塊,在電子電路設計中得到廣泛應用。目前,實現除法器的方法有硬件實現和軟件實現兩種方法。硬件實現的方法主要是以硬件的消耗為代價,從而有實現速度快的特點。用硬件的方

- 關鍵字:

Verilog 計算 精度可調 整數除法器

- 0 引 言

USB(通用串行總線)是英特爾、微軟、IBM、康柏等公司1994年聯合制定的一種通用串行總線規范,它具有數據傳輸速度快,成本低,可靠性高,支持即插即用和熱插拔等優點,迅速得到廣泛應用。

在高速的數

- 關鍵字:

Verilog FPGA USB 高速接口

- 針對機器人伺服控制系統高速度、高精度的要求,介紹一種全數字化的基于神經網絡控制的直流電機速度伺服控制系統的設計方案。速度控制器采用BP網絡參數辨識自適應控制,并將其在FPGA進行硬件實現;同時用Nios II軟核處理器作為上位機,構成一個完整的速度伺服控制器的片上可編程系統(SOPC)。實驗結果表明,該控制系統具有較高的控制精度、較好的穩定性和靈活性。

- 關鍵字:

SOPC 系統 控制器 速度 神經網絡 電機 基于 神經網絡 伺服控制 現場可編程門陣列 Verilog HDL

- 引言

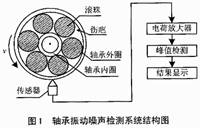

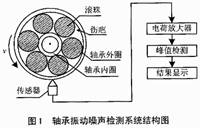

在軸承生產行業中,軸承振動噪聲的峰值檢測是一項重要的指標。以往,該檢測都是采用傳統的模擬電路方法,很難做到1:1地捕捉和保持較窄的隨機波形的最大正峰值。本文敘述了基于Verilog-HDL與高速A/D轉換器相結合所實現的快速軸承噪聲檢測方法。

1 振動噪聲電壓峰值檢測方案的確定

1.1 軸承振動噪聲的產生及檢測

圖1是軸承振動噪聲電壓峰值檢測系統的示意圖。由于加工設備、技術、環境等因素的影響,生產的軸承都程度不同地帶有傷疤。圖1中,假設某待測軸承有一處傷疤。由于傷痕的存在,軸

- 關鍵字:

Verilog 軸承 振動噪聲 電壓峰值檢測

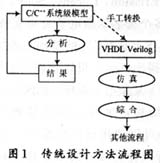

- 隨著集成電路制造技術的迅速發展,SOC設計已經成為當今集成電路設計的發展方向。SO C設計的復雜性對集成電路設計的各個層次,特別是對系統級芯片設計層次,帶來了新挑戰,原有的HDL難以滿足新的設計要求。

硬件設計領域有2種主要的設計語言:VHDL和Verilog HDL。而兩種語言的標準不統一,導致軟硬件設計工程師之間工作交流出現障礙,工作效率較低。因此,集成電路設計界一直在尋找一種能同時實現較高層次的軟件和硬件描述的系統級設計語言。Synopsys公司與Coware公司針對各方對系統級設計語言的

- 關鍵字:

SOC SystemC 集成電路 VHDL Verilog HDL

- 在現代IC設計中,特別是在模塊與外圍芯片的通信設計中,多時鐘域的情況不可避免。當數據從一個時鐘域傳遞到另一個域,并且目標時鐘域與源時鐘域不相關時,這些域中的動作是不相關的,從而消除了同步操作的可能性,并使系統重復地進入亞穩定狀態[1]。在有大量的數據需要進行跨時鐘域傳輸且對數據傳輸速度要求比較高的場合,異步FIFO是一種簡單、快捷的解決方案。

異步FIFO用一種時鐘寫入數據,而用另外一種時鐘讀出數據。讀寫指針的變化動作由不同的時鐘產生。因此,對FIFO空或滿的判斷是跨時鐘域的。如何根據異步的指針

- 關鍵字:

FIFO 異步 Verilog HDL IC 亞穩態

- 1.引言

隨著集成電路復雜度越來越高,測試開銷在電路和系統總開銷中所占的比例不斷上升,測試方法的研究顯得非常突出。目前在測試源的劃分上可以采用內建自測試或片外測試。內建自測試把測試源和被測電路都集成在芯片的內部,對于目前SOC級的芯片測試如果采用內建自測試則付出的硬件面積開銷則是很大的,同時也增加了芯片設計的難度:因此片外測試便成為目前被普遍看好的方法。由于FPGA具有可重構的靈活性,利用FPGA來作為測試源實現片外測試就是一種非常有效的手段。

由于偽隨機模式測試只需要有限個數的輸入向量便

- 關鍵字:

嵌入式系統 單片機 FPGA 序列生成器 Verilog HDL MCU和嵌入式微處理器

- 摘 要:本論文介紹視頻編解碼IP核在SOPC中的設計,用Verliog HDL實現其各個功能子模塊,全部調試仿真通過合并成一個模塊,實現了視頻信號的采集,分配,存儲以及色度空間的轉換。整個模塊都通過仿真實現與驗證,很好的達到了系統的要求。關鍵字:SOPC;視頻編解碼;IP核;Verilog HDL 引言 基于Nios II軟核的SOPC是Altera公司提出的片上可編程系統解決方案,它將CPU、存儲器、I/O接口、DSP模塊以及鎖相環的系統設

- 關鍵字:

嵌入式系統 單片機 SOPC 頻編解碼 SOPC 視頻編解碼 IP核 Verilog HDL

- 摘要:本文介紹一種嵌入式系統仿真方法,通過一種特殊設計的指令集仿真器ISS將軟件調試器軟件Keil uVision2和硬件語言仿真器軟件Modelsim連接起來,實現了軟件和硬件的同步仿真。

關鍵詞:BFM,TCL,Verilog,Vhdl,PLI,Modelsim,Keil uVision2,ISS,TFTP,HTTP,虛擬網卡,Sniffer,SMART MEDIA,DMA,MAC,SRAM,CPLD

縮略詞解釋:

BFM:總線功能模塊。在HDL

- 關鍵字:

BFM TCL Verilog Vhdl PLI Modelsim MCU和嵌入式微處理器

- 引言:數字濾波器是語音與圖像處理、模式識別、雷達信號處理、頻譜分析等應用中的一種基本的處理部件,它能滿足波器對幅度和相位特性的嚴格要求,避免模擬濾波器所無法克服的電壓漂移、溫度漂移和噪聲等問題。有限沖激響應(FIR)濾波器能在設計任意幅頻特性的同時保證嚴格的線性相位特性。

一、FIR數字濾波器

FIR濾波器用當前和過去輸入樣值的加權和來形成它的輸出,如下所示的前饋差分方程所描述的。

FIR濾波器又稱為移動均值濾波器,因為任何時間點的輸出均依賴于包含有最新的M個輸入樣值的一個窗。

- 關鍵字:

嵌入式系統 單片機 Verilog HDL FIR 數字濾波器 嵌入式

- 規范很重要

工作過的朋友肯定知道,公司里是很強調規范的,特別是對于大的設計(無論軟件還是硬件),不按照規范走幾乎是不可實現的。邏輯設計也是這樣:如果不按規范做的話,過一個月后調試時發現有錯,回頭再看自己寫的代碼,估計很多信號功能都忘了,更不要說檢錯了;如果一個項目做了一半一個人走了,接班的估計得從頭開始設計;如果需要在原來的版本基礎上增加新功能,很可能也得從頭來過,很難做到設計的可重用性。

在邏輯方面,我覺得比較重要的規范有這些: 1.設計必須文檔化。要將設計思路,詳細實現等寫入文檔,然

- 關鍵字:

verilog

verilog-a介紹

您好,目前還沒有人創建詞條verilog-a!

歡迎您創建該詞條,闡述對verilog-a的理解,并與今后在此搜索verilog-a的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473