- 隨著軟件無線電的發展。對于濾波器的處理速度要求越來越高。傳統的FIR濾波器一般采用通用DSP處理器,但是DSP處理器采用的是串行運算,而FPGA是現場可編程陣列,可以實現專用集成電路,另外還可以采用純并行結構

- 關鍵字:

FPGA FIR 濾波器

- FPGA開發中常用到單脈沖發生器。一些文章介紹過產生單脈沖的電路,產生的單脈沖脈寬和相位都不能與時鐘同步,只能用在要求不嚴格的場合。筆者目前從事的課題中需要一個與時鐘周期等寬,相位與時鐘周期相同的鍵

- 關鍵字:

FPGA 按鍵消抖 單脈沖 發生器電路

- 大多數軟、硬件工程師都很熟悉 FPGA,這點應該勿庸置疑。這種熟悉不見得是實質性的熟悉,而是從概念上比較了解,也就是說 FPGA 功能的快速發展和成本的不斷下降是大家都不容忽略的優勢。同時,他們也認識到這種可編程器件顯然能方便地作為各種數字電路以及邏輯處理的高靈活度、低成本的載體。

基本說來,在設計方案中發揮 FPGA 的功能就是簡單地映射出所需的邏輯,然后將其下載至適當容量大小的器件中。這有些像大型處理器系統主體設計的輔助支持工作,而且在該層面上也確實發揮著自身的支持性作用。

近期一些應

- 關鍵字:

SoC FPGA

- 設計基于FPGA的8段數碼管動態顯示IP核,介紹8段數碼管內部結構及其驅動顯示方式和IP核設計方法,給出8段數碼管動態顯示IP核的Verilog HDL程序源代碼及其C語言驅動程序。此IP核可例化成1~8個共陰極(或共陽極)數碼管控制器,能方便地控制1~8個數碼管同時顯示數字和小數點位。測試結果表明,該IP核工作可靠、穩定,可直接應用于電子設計中。

- 關鍵字:

FPGA 8段數碼管 動態顯示 IP核

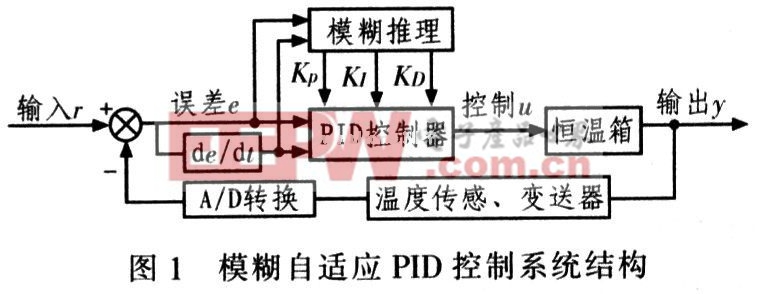

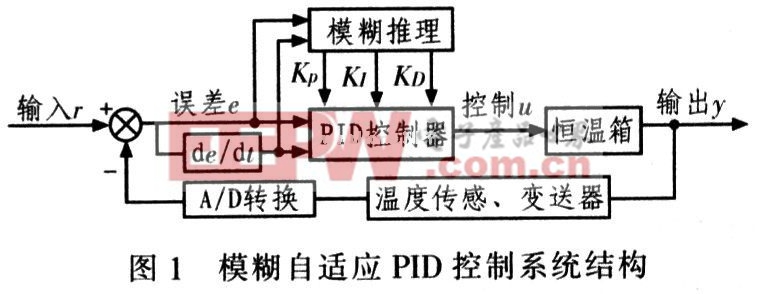

- 針對某恒溫箱控制系統中存在的非線性、時變等特點,結合傳統PID與現代模糊控制理論,以EP1C12型FP-GA為核心控制器,采用模塊化思想,設計并實現溫度模糊自適應PID控制。實際運行結果表明,采用該方法可明顯改善控制效果,在簡化設計的同時,也可提高系統的運算速度和可靠性。

- 關鍵字:

PID 控制器 設計 適應 模糊 FPGA 溫度 基于

- 1 引 言 同步在通信系統中占有非常重要的地位,同步系統性能的高低在很大程度上決定了通信系統的質量,甚至通信的成敗。相關器是同步系統的關鍵部件之一,因此,要求相關器須有比其它部件更高的可靠性。

- 關鍵字:

FPGA 數字相關器

- 0引言測頻和測脈寬現在有多種方法。通常基于MCU的信號參數測量,由于其MCU工作頻率很低,所以能夠達到...

- 關鍵字:

測量 脈沖信號 ADC FPGA

- 0引言隨著網絡流量的不斷增加和路由表容量的不斷增大,路由查找已經成為制約因特網的主要瓶頸。盡...

- 關鍵字:

FPGA 高速路由 查找 算法

- 可編程邏輯器件FPGA以其開發周期短、成本低、功耗低、可靠性高等優勢,廣泛應用于通信、航空、醫療等領域,近年來在消費電子領域中的應用也日漸增加。為進一步挖掘FPGA在家庭娛樂如游戲機開發與應用中的巨大商

- 關鍵字:

FPGA

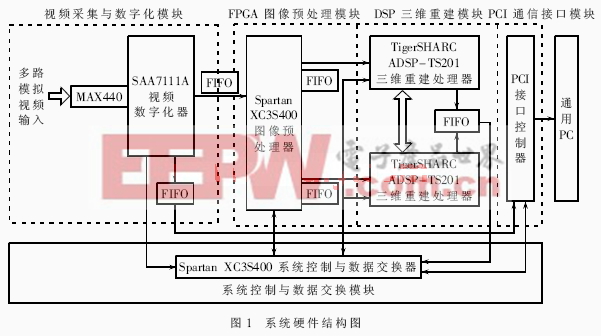

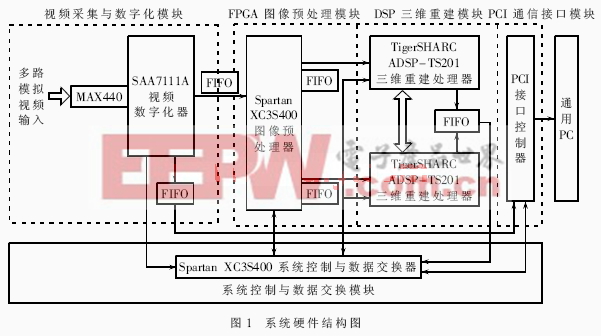

- 三維圖像信息處理FPGA+DSP核心架構的設計與實現,三維圖像信息處理一直是圖像視頻處理領域的熱點和難點,目前國內外成熟的三維信息處理系統不多,已有的系統主要依賴高性能通用PC完成圖像采集、預處理、重建、構型等囊括底層和高層的處理工作。三維圖像處理數據量特

- 關鍵字:

核心 架構 設計 實現 DSP FPGA 圖像 信息 處理 三維 FPGA dsp

- 根據國內主要寬帶運營商的要求及規劃,未來的發展依然會以EPON為主,包括10G和1G的EPON。為了應對國內接入網市場對于EPON產品形態的需求,我們基于芯片設計了一些不同形態的解決方案:包括能提供2路硬件解碼或軟件解碼的VoIPONU的參考設計;整合了4口以太網交換機的多用戶接入終端的參考設計;高密度16口、24口以太網交換機的MDU參考設計,以及計劃中的整合了16口IPPBX的參考設計等。

普然的10GEPON方案是一個基于FPGA的SoC(系統級芯片)MAC,其包涵一個強大的包處理引擎,從

- 關鍵字:

FPGA EPON SoC

- 在通信系統中分析計算系統抗噪聲性能時,經常假定信道噪聲為加性高斯型白噪聲(AGWN)。本文就是通過分析AGWN的性質,采用自頂向下的設計思路,將AGWN信號分成若干模塊,最終使用Verilog硬件描述語言,完成了通信

- 關鍵字:

FPGA AGWN 信號 生成器

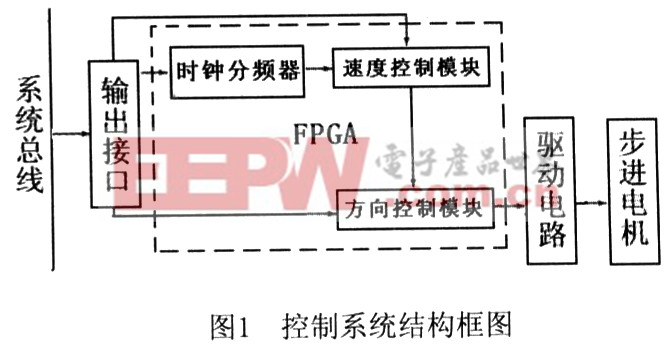

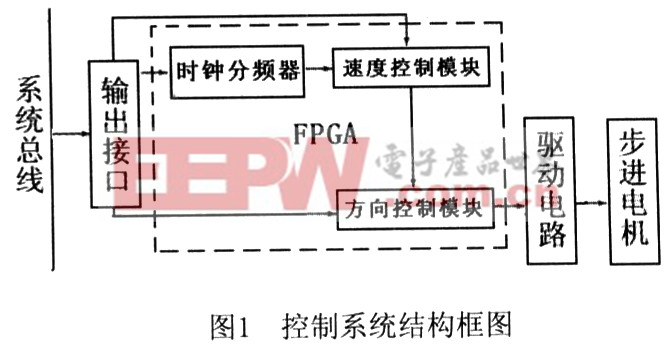

- 步進電機是一種將電脈沖轉化為角位移的執行機構。可以通過控制脈沖數來控制步進電機的角位移量,從而達到準確定位的目的,同時可以通過控制脈沖頻率來控制電機的速度和加速度,從而達到調速的目的。由于步進電機

- 關鍵字:

應用 控制 電機 步進 FPGA FPGA 控制系統 步進電機 電機鐵芯

- 0 引言

高速數字化采集技術和FPGA技術的發展已經對傳統測試儀器產生了深刻的影響。數字存儲示波器(DS0)是模擬示波器技術、數字化測量技術、計算機技術的綜合產物,他主要以微處理器、數字存儲器、A/D轉換器和D

- 關鍵字:

FPGA 數字存儲示 波器設計

- O 引言

作戰系統時間的統一同步(時統)的重要性越來越得到重視,只有保證整個系統處在同一時間的基準上,才能實現真正意義上的以網絡為中心的信息戰、以精確制導武器系統對抗和以協同作戰方式為主的現代化戰爭。

- 關鍵字:

FPGA 系統

fpga-spartan介紹

您好,目前還沒有人創建詞條fpga-spartan!

歡迎您創建該詞條,闡述對fpga-spartan的理解,并與今后在此搜索fpga-spartan的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473