基于FPGA的簡易數字存儲示波器設計

0 引言

高速數字化采集技術和FPGA技術的發展已經對傳統測試儀器產生了深刻的影響。數字存儲示波器(DS0)是模擬示波器技術、數字化測量技術、計算機技術的綜合產物,他主要以微處理器、數字存儲器、A/D轉換器和D/A轉換器為核心,輸入信號首先經A/D轉換器轉換成數字信號,然后存儲在RAM中,需要時再將RAM中的內容讀出,經D/A轉換器恢復為模擬信號顯示在示波器上,或者通過接口與計算機相連對存儲的信號作進一步處理,這樣可大大改進顯示特性,增強功能,便于控制和智能化。這種DSO中看到的波形是由采集到的數據經過重構后得到的波形,而不是加到輸入端上信號的波形。本文采用基于FPGA的方式進行數據采集、數據處理等功能的設計。這種設計方案在高速數據采集上具有很多優點,如體積小、功耗低、時鐘頻率高、內部延時小、全部控制邏輯由硬件完成等,另外編程配置靈活、開發周期短、利用硬件描述語言來編程,可實現程序的并行執行,這將會大大提高系統的性能,有利于在系統設計和現場運行后對系統進行修改、調試、升級等。

1 系統實現方案

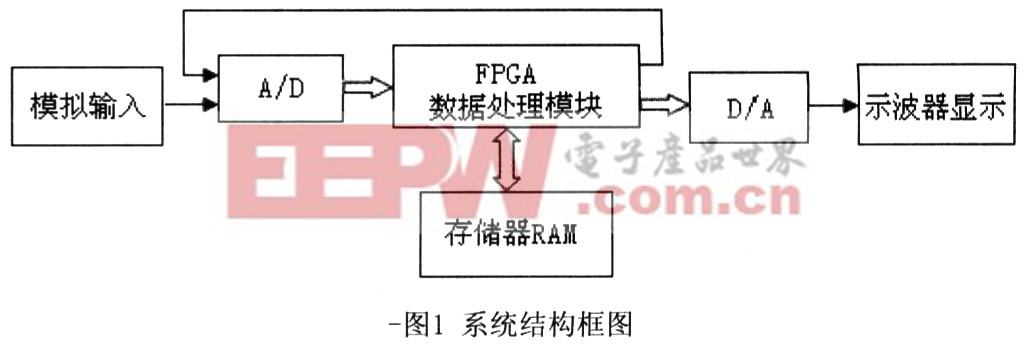

根據設計指標要求,基于FPGA的系統結構如圖1所示,主要由模數轉換、數模轉換、FPGA數據處理、數據存儲四部分組成。由垂直分辨率大于或等于32點/div可知A/D、D/A轉換器至少8位,系統選用AD976(16位A/D轉換器)和AD669(16位D/A轉換器),由于受PLC I/0口數量的影響,AD976和DA669使用其中13位,RAM選HM6264(64k),時鐘采用125kHz,PLC選用EPFl0K10LC84一3。模擬信號通過A/D轉換器將信號輸入給FPGA,FPGA根據相關指令進行數據存儲至RAM或將數據從RAM讀出送給D/A轉換器轉換成模擬信號輸出。

2 系統主要電路

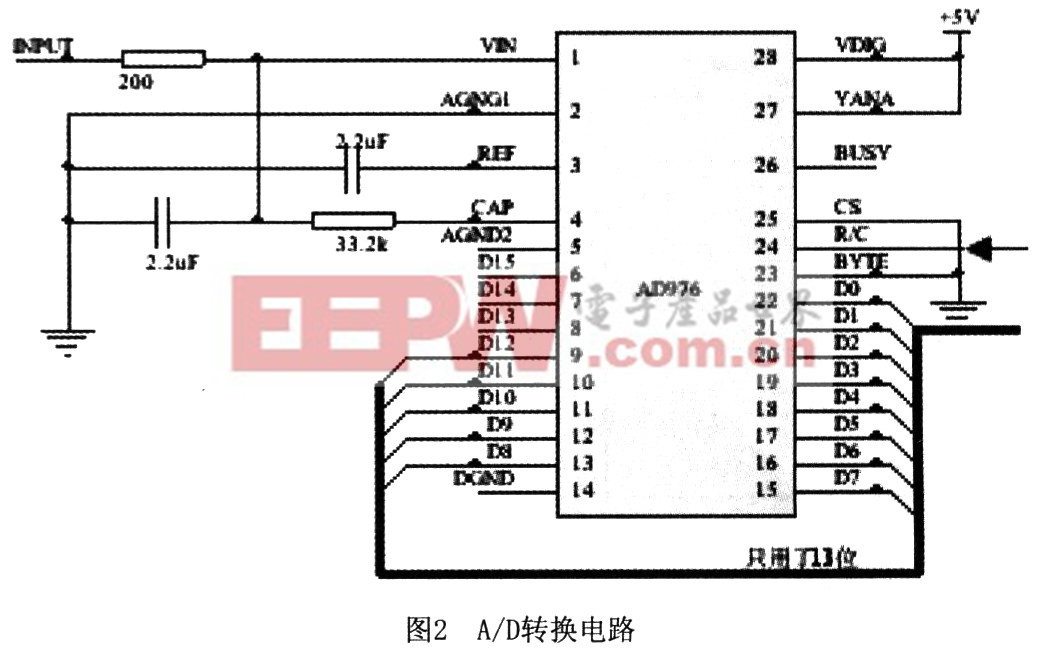

系統中FPGA數據處理模塊將A/D輸入、RAM數據存儲和D/A輸出連接在一起,實現信號的傳遞、存儲等控制。輸入電路中A/D轉換芯片選用AD公司的AD976,它是16位高速,高精度A/D轉換器,最大采集率為100kSPS,輸入信號范圍為一10~+10V,R/C為讀數/轉換控制端,CS為片選端,電路連接如圖2所示。

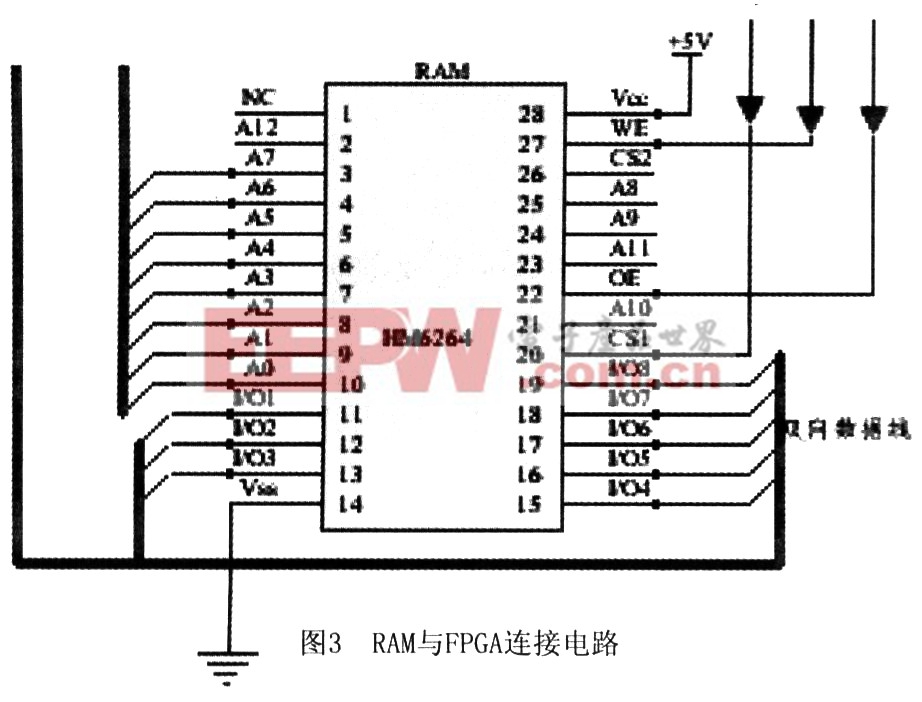

數據存儲器HM6264是64k的靜態SRAM,8位I/0公共輸入/出線,13位地址線,三態輸出。地址有效條件是/CSl=0,CS2=ln/WE=0,/OE=1執行寫操作;/WE=1,/OE=O執行讀操作。電路連接如圖3所示。

輸出電路中D/A轉換芯片AD669也是AD公司推出的16位高速,高精度D/A轉換器,具有高性價比,電路連接如圖4所示。

評論