fpga+mpu+mcu 文章 最新資訊

基于FPGA的圖像實(shí)時(shí)處理系統(tǒng)設(shè)計(jì)

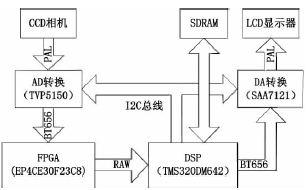

- 由于現(xiàn)場實(shí)時(shí)測量的需要,機(jī)器視覺技術(shù)越來越多地借助硬件來完成,如DSP芯片、專用圖像信號處理卡等。但是,DSP做圖像處理也面臨著由于數(shù)據(jù)存儲與處理量大,導(dǎo)致處理速度較慢,系統(tǒng)實(shí)時(shí)性較差的問題。本文將FPGA的IP核內(nèi)置緩存模塊和乒乓讀寫結(jié)構(gòu)相結(jié)合,實(shí)現(xiàn)了圖像數(shù)據(jù)的緩存與提取,節(jié)省了存儲芯片所占用的片上空間,并且利用圖像預(yù)處理重復(fù)率高,但算法相對簡單的特點(diǎn)和FPGA數(shù)據(jù)并行處理,結(jié)合流水線的結(jié)構(gòu),大大縮短了圖像預(yù)處理的時(shí)間,解決了圖像處理實(shí)時(shí)性差的問題。 1系統(tǒng)架構(gòu)和流程簡介 本系統(tǒng)采用了F

- 關(guān)鍵字: FPGA DSP

雷達(dá)信號處理:FPGA還是GPU?

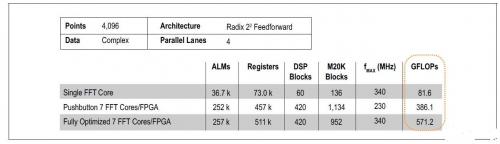

- FPGA和CPU一直是雷達(dá)信號處理不可分割的組成部分。傳統(tǒng)上FPGA用于前端處理,CPU用于后端處理。隨著雷達(dá)系統(tǒng)的處理能力越來越強(qiáng),越來越復(fù)雜,對信息處理的需求也急劇增長。為此,F(xiàn)PGA不斷在提高處理能力和吞吐量,CPU也在發(fā)展以滿足下一代雷達(dá)的信號處理性能需求。這種努力發(fā)展的趨勢導(dǎo)致越來越多的使用CPU加速器,如圖形處理單元(GPU)等,以支持較重的處理負(fù)載。 本文對比了FPGA和GPU浮點(diǎn)性能和設(shè)計(jì)流程。最近幾年,GPU已經(jīng)不僅能完成圖形處理功能,而且成為強(qiáng)大的浮點(diǎn)處理平臺,被稱之為GP-

- 關(guān)鍵字: FPGA GPU

醫(yī)療電子平臺選擇:FPGA、ARM、X86、DSP還是GPU分析

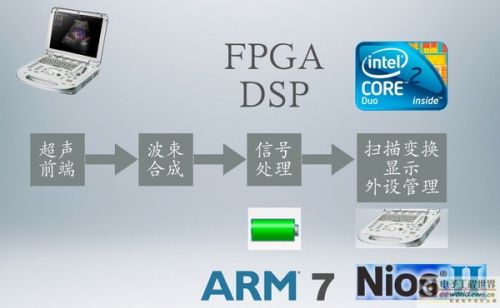

- “邁瑞對于處理器平臺的選擇有兩個(gè)看似矛盾的原則:‘多’和‘少’。其中‘多’是指多樣性,我們知道無論是DSP、ARM、X86還是FPGA、GPU,每個(gè)平臺都有各自的優(yōu)點(diǎn)和缺陷,因此在設(shè)計(jì)產(chǎn)品時(shí)就可以根據(jù)他們的特點(diǎn)進(jìn)行選擇和搭配,處理器平臺的多樣性以及合理的搭配可以使產(chǎn)品更具有競爭力。”在日前舉辦的第三屆中國國際醫(yī)療電子技術(shù)大會(CMET2010)上,深圳邁瑞生物醫(yī)療電子硬件技術(shù)委員會執(zhí)行主任、系統(tǒng)工程師姚力與

- 關(guān)鍵字: FPGA ARM

基于FPGA 的太陽能并網(wǎng)逆變器的研究

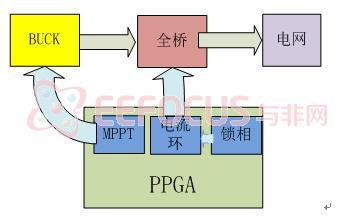

- 系統(tǒng)概述 新能源發(fā)電成為21世紀(jì)解決能源危機(jī)的必經(jīng)出路,光伏發(fā)電、風(fēng)電、核電等新能源發(fā)電是目前新能源發(fā)電研究的幾大方向。這幾種新能源各有各的特點(diǎn),我們選擇了最靠近我們的光伏發(fā)電作為研究出發(fā)點(diǎn)。 目前光伏發(fā)電并網(wǎng)技術(shù)的研究愈加深入成熟,而關(guān)于光伏發(fā)電技術(shù)的具體應(yīng)用環(huán)節(jié)還是有著許多發(fā)揮余地。光伏發(fā)電的優(yōu)點(diǎn)是清潔安全、分布相對較為均勻、可持續(xù)利用。同時(shí)光伏發(fā)電也存在自己的問題,其中一個(gè)很重要的問題是光伏發(fā)電需要做的是收集輻射到地表的太陽能,這個(gè)環(huán)節(jié)需要占用大量的空間,這個(gè)問題使光伏發(fā)電的應(yīng)用有著

- 關(guān)鍵字: FPGA 逆變器

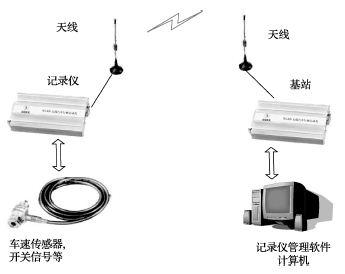

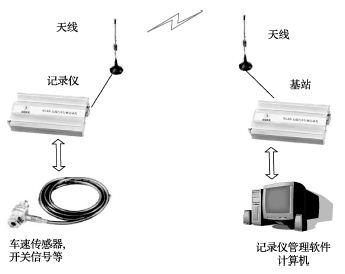

基于MCU的無線行駛記錄儀硬軟件設(shè)計(jì)

- 1引言 汽車行駛記錄儀是一種在汽車上使用的記錄裝置。此設(shè)備能對車輛的行駛速度、里程以及有關(guān)車輛行駛的其他狀態(tài)信息進(jìn)行記錄存儲并可通過接口實(shí)現(xiàn)數(shù)據(jù)輸出。無線行駛記錄儀把無線通信方式與汽車行駛記錄儀結(jié)合,實(shí)現(xiàn)記錄儀功能的同時(shí)方便用戶對數(shù)據(jù)的讀取和信息處理,可解決傳統(tǒng)記錄儀通過U盤等介質(zhì)導(dǎo)取數(shù)據(jù)的弊端。 無線通信有多種方式,其中在工業(yè)應(yīng)用領(lǐng)域應(yīng)用最廣泛的有ZigBee無線通信,RF無線通信和Wi‐Fi無線通信。ZigBee主要用于傳輸?shù)蛿?shù)據(jù)率的通信,具有超低的功率損耗,主要目標(biāo)是提供設(shè)備控制信道

- 關(guān)鍵字: MCU 行駛記錄儀

基于MCU的無線行駛記錄儀硬軟件設(shè)計(jì)

- 1引言 汽車行駛記錄儀是一種在汽車上使用的記錄裝置。此設(shè)備能對車輛的行駛速度、里程以及有關(guān)車輛行駛的其他狀態(tài)信息進(jìn)行記錄存儲并可通過接口實(shí)現(xiàn)數(shù)據(jù)輸出。無線行駛記錄儀把無線通信方式與汽車行駛記錄儀結(jié)合,實(shí)現(xiàn)記錄儀功能的同時(shí)方便用戶對數(shù)據(jù)的讀取和信息處理,可解決傳統(tǒng)記錄儀通過U盤等介質(zhì)導(dǎo)取數(shù)據(jù)的弊端。 無線通信有多種方式,其中在工業(yè)應(yīng)用領(lǐng)域應(yīng)用最廣泛的有ZigBee無線通信,RF無線通信和Wi‐Fi無線通信。ZigBee主要用于傳輸?shù)蛿?shù)據(jù)率的通信,具有超低的功率損耗,主要目標(biāo)是提供設(shè)備控制信道

- 關(guān)鍵字: MCU ZigBee

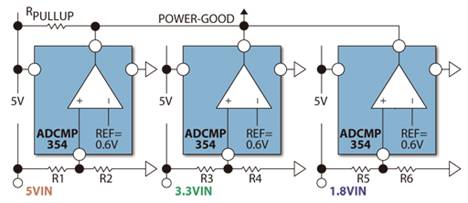

混合信號IC──復(fù)雜電源管理組件的設(shè)計(jì)挑戰(zhàn)及解決方案

- 隨著系統(tǒng)內(nèi)電源數(shù)量的增多,為了確保其安全、經(jīng)濟(jì)、持續(xù)和正常的工作,對電源軌進(jìn)行監(jiān)測和控制變得非常重要,特別是在使用微處理器時(shí)。確定電壓軌是否處于工作范圍內(nèi),以及該電壓相對于其它電壓軌是否按照正確的時(shí)序上電或斷電,這些對于系統(tǒng)執(zhí)行的可靠性和安全性來說都是至關(guān)重要的。例如FPGA,在向組件提供5V I/O(輸入/輸出)電壓之前,必須先施加3.3V的核心電壓,并持續(xù)至少20ms,以避免組件上電時(shí)受到損壞。對于系統(tǒng)的可靠性來說,滿足這樣的時(shí)序要求就像要保證組件在規(guī)定的電源電壓和溫度范圍內(nèi)工作一樣至關(guān)重要。

- 關(guān)鍵字: FPGA DSP

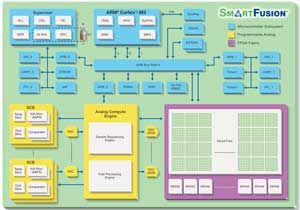

混合信號FPGA實(shí)現(xiàn)真正單芯片SOC

- 要實(shí)現(xiàn)能夠?qū)⑺兄匾δ芗稍趩我黄骷脑O(shè)計(jì)理由很簡單,因?yàn)檫@樣就能將材料成本、部件庫存及電路板面積減至最低。另外,相較于多芯片解決方案,單芯片方案的功耗也較低,同時(shí)也有助于提高對知識產(chǎn)權(quán)的保護(hù)。如果一項(xiàng)設(shè)計(jì)功能的精髓能夠深植于單一芯片上,將會大大增加第三方取得這項(xiàng)設(shè)計(jì)的困難度。 單芯片系統(tǒng)對嵌入式系統(tǒng)設(shè)計(jì)師來說,往往會隨著其面對的不同的系統(tǒng)設(shè)計(jì)而各有不同。例如,在龐大的娛樂或通信消費(fèi)產(chǎn)品市場中,SoC意味著一顆具有數(shù)百萬邏輯門的集成電路(IC),其中包含許多大型定制邏輯模塊,并有將芯片的數(shù)字處

- 關(guān)鍵字: FPGA SOC

物聯(lián)網(wǎng)開創(chuàng)潛力股促進(jìn)MCU、無線IC和感測器出貨猛漲

- 物聯(lián)網(wǎng)邁向多元無線接取、低功耗智慧控制/感測設(shè)計(jì)的趨勢日益明朗,將促進(jìn)MCU、無線通訊IC和感測器出貨量涌現(xiàn)一波接一波漲勢;半導(dǎo)體廠商亦看好這三類晶片將成為物聯(lián)網(wǎng)的明星方案,競相啟動新技術(shù)投資及產(chǎn)品開發(fā)計(jì)畫。 物聯(lián)網(wǎng)IC潛力股“漲”聲不斷。在穿戴裝置、車聯(lián)網(wǎng)、工控自動化和智慧家庭等物聯(lián)網(wǎng)應(yīng)用需求帶動下,32位元微控制器(MCU)、低功耗無線通訊IC,以及微機(jī)電系統(tǒng)(MEMS)感測器的出貨量正持續(xù)翻漲,相關(guān)晶片業(yè)者皆可望雨露均霑。 尤其今年開年以來,各個(gè)物聯(lián)網(wǎng)應(yīng)用山頭

- 關(guān)鍵字: 物聯(lián)網(wǎng) MCU

Mentor Graphics 宣布推出旨在提升測試平臺效率的 EZ-VIP 包

- Mentor Graphics公司今天宣布即時(shí)推出 EZ-VIP 效率包。該效率包面向使用 Questa® Verification IP (QVIP) 的 ASIC 和 FPGA 驗(yàn)證團(tuán)隊(duì),可將創(chuàng)建、實(shí)例化、配置和連接 QVIP 測試平臺的時(shí)間縮短 5 倍以上,從而顯著提高效率。這就意味著,驗(yàn)證團(tuán)隊(duì)可以將更多的時(shí)間花在 QVIP 上,以驗(yàn)證他們的設(shè)計(jì)在功能上是否正確。 EZ-VIP 包由 QVIP 配置軟件、一個(gè) VIP 調(diào)通服務(wù)包和一個(gè)全新的 EZ-VIP API 組成。其中,QVI

- 關(guān)鍵字: Mentor Graphics FPGA

【從零開始走進(jìn)FPGA】 玩轉(zhuǎn)VGA

- 一、VGA的誘惑 首先,VGA的驅(qū)動,這事,一般的單片機(jī)是辦不到的;由于FPGA的速度,以及并行的優(yōu)勢,加上可現(xiàn)場配置的優(yōu)勢,VGA的配置,只有俺們FPGA可以勝任,也只有FPGA可以隨心所欲地配置(當(dāng)然ARM也可以,應(yīng)用比較高吧)。 初學(xué)者就是喜歡看炫的效果,往往會忍不住想玩。尤其玩FPGA的,沒玩VGA就感到跟單片機(jī)沒啥提升,因此VGA的驅(qū)動也不得不講。Bingo當(dāng)年也是如此。擋不住VGA的誘惑,初學(xué)者問Bingo VGA問題的人也是灰常的多,也許一般教科書理論太強(qiáng),實(shí)際應(yīng)用不是很身后

- 關(guān)鍵字: VGA FPGA

Altera宣布Stratix 10的創(chuàng)新全面刷新高端FPGA和SoC業(yè)界性能指標(biāo)記錄

- Altera公司今天發(fā)布其Stratix® 10 FPGA和SoC體系結(jié)構(gòu)和產(chǎn)品細(xì)節(jié),這一下一代高端可編程邏輯器件在性能、集成度、密度和安全特性方面實(shí)現(xiàn)全面突破,勢必將云時(shí)代的網(wǎng)絡(luò)通信技術(shù)推向又一個(gè)巔峰。 Stratix 10 FPGA和SoC采用了Altera革命性的HyperFlex™ FPGA架構(gòu),由Intel® 14 nm三柵極工藝技術(shù)制造,內(nèi)核性能是前一代FPGA的2倍。業(yè)界性能最好、密度最高、具有先進(jìn)的嵌入式處理功能的FPGA與GPU級別浮點(diǎn)計(jì)算性能和異構(gòu)

- 關(guān)鍵字: Altera FPGA

FPGA開發(fā)外設(shè)子板模塊電路設(shè)計(jì)詳解

- FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。FPGA的開發(fā)相對于傳統(tǒng)PC、單片機(jī)的開發(fā)有很大不同。FPGA以并行運(yùn)算為主,以硬件描述語言來實(shí)現(xiàn);相比于PC或單片機(jī)(無論是馮諾依曼結(jié)構(gòu)還是哈佛結(jié)構(gòu))的順序操作有很大區(qū)別,也造成了FPGA開發(fā)入門較難。目前國內(nèi)有專

- 關(guān)鍵字: FPGA A/D

fpga+mpu+mcu介紹

您好,目前還沒有人創(chuàng)建詞條fpga+mpu+mcu!

歡迎您創(chuàng)建該詞條,闡述對fpga+mpu+mcu的理解,并與今后在此搜索fpga+mpu+mcu的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fpga+mpu+mcu的理解,并與今后在此搜索fpga+mpu+mcu的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司