英特爾收購阿爾特拉,發布向GPU的宣戰宣言——新FPGA

美國阿爾特拉公司(Altera)發布了預定于2015年底供應樣品的高端FPGA“Stratix 10”的詳情。Stratix 10由2015年6月1日(美國時間)宣布收購阿爾特拉的美國英特爾公司代工,是利用14nm工藝制造的FPGA。

本文引用地址:http://www.104case.com/article/275499.htmStratix 10雖然以前就公布了概要,但披露器件產品線等詳情還是首次。預定于2015年第四季度供應樣品。

圖1:接受《日經電子》采訪的阿爾特拉產品營銷高級總監Patrick Dorsey

Stratix 10通過改善FPGA架構,將實現該公司以往產品“Stratix V”約2倍的性能。不僅在邏輯元件(LE)內,還在LE外部的布線部分設置幾百萬個寄存器,將管道細分,視用戶邏輯的類型,最大工作頻率可達900MHz左右。

Stratix 10與已經在供應樣品的該公司的中檔FPGA“Arria 10”一樣,DSP硬宏支持浮點運算。最多的品種配備1.1萬個以上的DSP硬宏,浮點運算性能超越美國英偉達的GPU、高達10TFLOPS。該公司的產品營銷高級總監Patrick Dorsey說:“我們的產品已經可以與英偉達的GPU展開全面競爭”,顯露出對GPU的競爭意識。

與賽靈思在發展方向上的差異明確

Stratix 10的特點主要有4個:(1)實現Stratix V約2倍性能的“HyperFlex架構”;(2)耗電量的削減;(3)采用英特爾的2.5D封裝技術;(4)考慮到云端多租戶使用的安全功能。

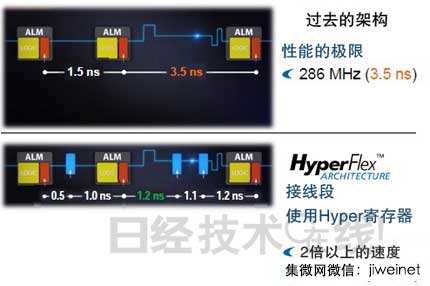

(1)的HyperFlex架構,是類似于微處理器的超級管道技術。是細分管道,增加段數,使其能以更高的時鐘頻率工作的技術。

具體來說,Stratix 10在接線段設置了專用的“Hyper寄存器”。使用該Hyper寄存器,將細分管道以提高頻率。而一般的FPGA,寄存器只配置在LE內,接線段是不配置寄存器的。

圖2:利用Hyper寄存器細分管道

據稱,因Hyper寄存器的插入,是由編譯器端自動進行的,邏輯電路設計者無需顧慮。阿爾特拉2015年5月發布的新設計工具“Quartus II”,配備了實現這一操作的功能。

按照該公司的估算,某無線通信基礎設施用電路,Stratix V的最大工作頻率為491MHz,而Stratix 10則為982MHz。在數據中心用的加速電路,Stratix V的最大工作頻率為156MHz,而Stratix 10為452MHz。

圖3:與Stratix V相比的高速化程度

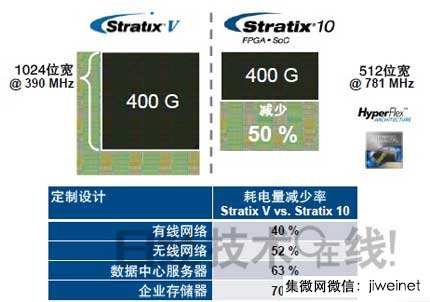

關于(2),與Stratix V相比,Stratix 10的耗電量最大可減少70%。除利用14nm工藝制造技術,降低了電源電壓外,與Stratix V相比,還能以較窄的位寬實現相同的性能,據稱這也有助于降低耗電量。

圖4:與Stratix V相比減少的耗電量

圖5:數據中心的使用示例

利用2.5D封裝分離PHY,為與Xeon整合作準備?

(3)利用了代工商英特爾的2.5D封裝技術“EMIB(Embedded Multi-die Interconnect Bridge)”(參閱本站報道)。

英特爾的競爭對手——美國賽靈思公司(Xilinx)也在使用2.5D封裝技術,但阿爾特拉和賽靈思的使用方式完全不同。

賽靈思是把FPGA架構分成數枚芯片,用內插器連接。而阿爾特拉的戰略,則是FPGA架構封裝在單一芯片中,收發器電路按照不同接口,準備不同的芯片。阿爾特拉把這種芯片叫作“區塊”(Tile)。

圖6:區塊的示意圖

阿爾特拉將收發器電路作為單獨芯片的理由主要有兩個。一是為了方便支持今后可能面世的新一代高速接口。在支持對PCI Express Gen 4等數據速率的高速化,以及含光通信在內等新調制方式時,分芯片更容易替換,實現起來方便。

另一個是FPGA架構收納在單一芯片中,LE之間的通信“不像賽靈思那樣,無需經由不同的內插器,可以提高可靠性”(Dorsey)。賽靈思和阿爾特拉最近在片上存儲器、浮點運算等許多方面,戰略上的差異逐漸明確,2.5D封裝的利用方法也明顯不同。

阿爾特拉將收發器電路另分芯片,也可以看作是與英特爾的服務器微處理器“Xeon”整合之前的準備。英特爾在宣布收購阿爾特拉之前,一直在計劃推出將Xeon與FPGA集成于同一封裝的產品。通過像英偉達GPU配備的接口“NVLINK”那樣,使在FPGA端容易配備可以與CPU高速連接的接口,以提高其作為加速器的利用價值。關于這一點,阿爾特拉的Dorsey表示“無可奉告”。

立足云端使用,FPGA終將實現多租戶化

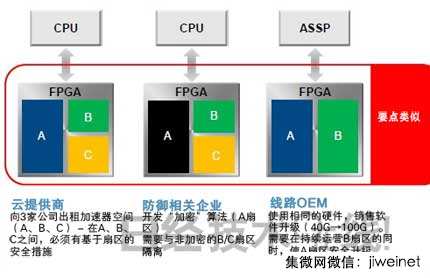

關于(4),Stratix 10加入了用來防范非法訪問、防范篡改等的“安全設備管理器(SDM)”技術。在芯片內設置約15~150個扇區并予以隔離,使扇區可以單獨配置和認證。

作為扇區的使用示例,阿爾特拉舉出了防御設備中加密算法的隱藏、無線通信基礎設施設備中特定電路的更新(在持續使用特定電路的同時,更新其他部分的電路)等。在該公司列舉的示例中,最有特點的當屬云服務的例子。

具體來說,就是云服務運營商在自己的基礎設施中采用FPGA,把單一FPGA器件分割為多個扇區,出租給多位客戶的使用形態。

這就像是在云計算領域,多家用戶企業共用同一系統的“多租戶”。可以說象征了“重視數據中心用途”這一阿爾特拉的現行發展方向。

圖7:將單一FPGA分割使用的“扇區”使用示例

最左側的云端“多租戶”使用象征著阿爾特拉如今的發展方向

美國微軟計劃于2015年下半年,將為本公司數據中心大量引進FPGA,用來提高搜索引擎的速度,提供基于深度學習(CNN)的圖像識別。

估計微軟也在考慮把引進的大量FPGA,經由該公司的云服務“Azure”出租給客戶。Stratix 10規模最大的品種配備550萬個LE。達到如此規模后,在單一FPGA中劃分區域,提供給多個應用、多家企業共用的利用形式便成為了可能。

PUF電路為Intrinsic ID制造

Stratix 10為加強防篡改性、加密密鑰等,在高端FPGA中首次配備了PUF(physical unclonable function)電路。PUF電路是利用半導體制造誤差造成的微小個體差異,生成芯片固有ID的技術。采用的PUF電路為荷蘭Intrinsic ID公司制造。

配備PUF的FPGA此前美國美高森美公司(Microsemi)曾推出過,“在賽靈思和阿爾特拉的高端FPGA中配備,估計Stratix 10還是第一個”(Dorsey)。

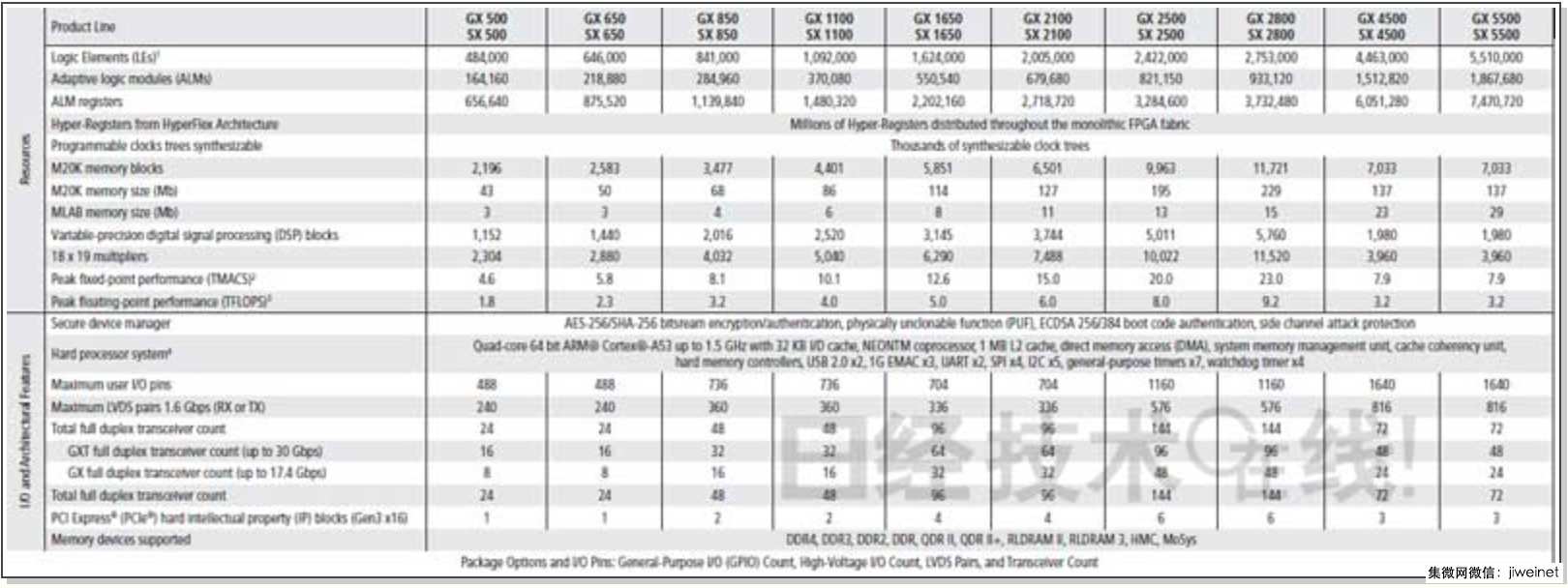

ARM內核也實現64位化

Stratix 10與以往產品一樣,也將準備配備ARM內核的“Stratix 10 SoC”。阿爾特拉的FPGA過去一直配備32位ARM內核,Stratix 10 SoC將配備64位四核“Cortex-A53”。最大工作頻率為1.5GHz。(記者:進藤智則,日經Robotics)

圖8:Stratix 10的品種一覽

fpga相關文章:fpga是什么

評論