基于FPGA的圖像實時處理系統(tǒng)設計

由于現(xiàn)場實時測量的需要,機器視覺技術(shù)越來越多地借助硬件來完成,如DSP芯片、專用圖像信號處理卡等。但是,DSP做圖像處理也面臨著由于數(shù)據(jù)存儲與處理量大,導致處理速度較慢,系統(tǒng)實時性較差的問題。本文將FPGA的IP核內(nèi)置緩存模塊和乒乓讀寫結(jié)構(gòu)相結(jié)合,實現(xiàn)了圖像數(shù)據(jù)的緩存與提取,節(jié)省了存儲芯片所占用的片上空間,并且利用圖像預處理重復率高,但算法相對簡單的特點和FPGA數(shù)據(jù)并行處理,結(jié)合流水線的結(jié)構(gòu),大大縮短了圖像預處理的時間,解決了圖像處理實時性差的問題。

本文引用地址:http://www.104case.com/article/276158.htm1系統(tǒng)架構(gòu)和流程簡介

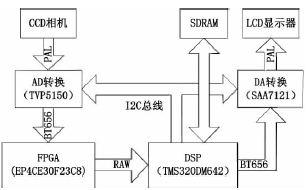

本系統(tǒng)采用了FPGA與DSP相結(jié)合的架構(gòu),綜合了各自的優(yōu)點,使系統(tǒng)滿足實時性要求的同時,又可以在后續(xù)任務中完成復雜算法的處理。系統(tǒng)的整體架構(gòu)如圖1所示。

系統(tǒng)上電后,CCD相機向AD轉(zhuǎn)換芯片TVP5150輸入PAL制式模擬圖像信號,TVP5150將模擬信號轉(zhuǎn)換成數(shù)字信號后,以ITU-R BT656格式傳輸?shù)紽PGA,F(xiàn)PGA對采集到的ITU-R BT656格式的圖像數(shù)據(jù)去消隱化后進行預處理,處理完之后傳輸?shù)紻M642的VP0口,VP0以8位RAW格式接收圖像數(shù)據(jù),并通過EDMA通道存儲到連接在EMIFA接口上的SDRAM中。經(jīng)過DSP的圖像處理后,將SDRAM中的圖像數(shù)據(jù)以ITU-R BT656的格式經(jīng)DM642的VP2口傳輸?shù)紻A芯片SAA7121,然后SAA7121進行DA轉(zhuǎn)換后,將PAL制式的模擬信號輸出到LCD顯示器上顯示。需要說明的是,TVP5150和SAA7121通過DM642的I2C總線接口配置。

圖1系統(tǒng)結(jié)構(gòu)框圖

2 FPGA圖像緩存與處理

由于該系統(tǒng)利用FPGA并行性和高速性來縮減圖像預處理的時間,因此,F(xiàn)PGA的圖像緩存和預處理環(huán)節(jié)直接影響到系統(tǒng)的實時性,是整個系統(tǒng)的核心部分,也是本文所要介紹的重點。根據(jù)圖像預處理的需求和FPGA內(nèi)部各模塊功能的不同,將其分為4個部分:去消隱化、濾波、閾值分割和邊緣提取。

2.1去消隱化

FPGA接收TVP5150傳輸?shù)臄?shù)字信號為ITUR BT656格式,該格式除了傳輸4∶2∶2的YCbCr視頻數(shù)據(jù)流外,還包含行、列消隱信號。因此,需要將行列消隱信號剔除掉,以便后期進行圖像預處理。

根據(jù)BT656的固有結(jié)構(gòu),編寫了Verilog硬件語言程序,用于提取BT656中的720×576個像素點的有效視頻數(shù)據(jù),由于圖像處理過程只需要檢測亮度信號(Y分量),因此同時舍去各像素點的色度信號(Cb、Cr分量),僅保留亮度信號作為圖像有效數(shù)據(jù)。在去消隱化過程中,每行起始狀態(tài)里,檢測輸入8位數(shù)據(jù),如果連續(xù)3個輸入信號滿足FF、00、00結(jié)構(gòu),則跳入下一個狀態(tài),判斷下一個8位輸入XY信號,是否為有效圖像標志信號(80標志該行為偶場圖像數(shù)據(jù),C7標志該行為奇場圖像數(shù)據(jù)),若判斷是,則計數(shù)器計數(shù),并采集計數(shù)器為偶數(shù)時的數(shù)據(jù)(即亮度信號),為圖像有效數(shù)據(jù),當采集滿720個圖像有效數(shù)據(jù)時,狀態(tài)機轉(zhuǎn)入初始狀態(tài)繼續(xù)等待FF、00、00結(jié)構(gòu),并依此循環(huán)。

2.2濾波

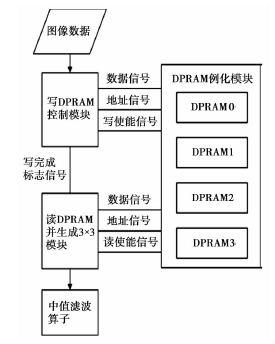

攝像機采集的圖像存在各類噪聲,從而對目標信息的進一步處理產(chǎn)生不利影響,因此,獲取圖像后需要對圖像進行濾波。考慮到中值濾波在平滑脈沖噪聲方面非常有效,并且可以保護圖像尖銳的邊緣的優(yōu)點,我們選用3×3中值濾波作為系統(tǒng)的圖像濾波算法。中值濾波模塊包括3個子模塊:乒乓結(jié)構(gòu)讀寫模塊、3×3陣列生成模塊和中值濾波算子模塊,其流程如圖2所示。

圖2中值濾波模塊流程圖

2.2.1乒乓結(jié)構(gòu)讀寫模塊

為了節(jié)約芯片成本和電路板的片上空間,圖像數(shù)據(jù)的存儲利用FPGA上固有的IP核生成雙口RAM來緩存。由于圖像數(shù)據(jù)量較大,而中值濾波只需要持續(xù)地提取3×3模塊來進行數(shù)據(jù)處理,因此,僅需生成4片雙口RAM,每個用于存儲一行的圖像數(shù)據(jù),通過乒乓讀寫結(jié)構(gòu),便可實現(xiàn)數(shù)據(jù)的緩存。

乒乓讀寫結(jié)構(gòu)是指將輸入數(shù)據(jù)流通過輸入數(shù)據(jù)選擇單元等時地將輸入數(shù)據(jù)分配到兩個數(shù)據(jù)緩存區(qū),并且再寫入某一個緩存區(qū)的過程中,從另外一個緩存區(qū)讀出上個緩存周期寫入的數(shù)據(jù),依此循環(huán),不斷往復。在本系統(tǒng)中,選用4片1024×8bit的雙口RAM作為緩存區(qū),在每個緩存周期,向其中1片雙口RAM中寫入圖像數(shù)據(jù),同時,讀控制模塊從另外3片雙口RAM中讀出前三個緩存周期已寫入的數(shù)據(jù),用于生成3×3陣列。當一行數(shù)據(jù)緩存完成后,寫使能信號跳轉(zhuǎn)到下一個雙口RAM,繼續(xù)進行下一行數(shù)據(jù)寫入,讀控制模塊繼續(xù)讀取剩余三行所存儲數(shù)據(jù)。

2.2.2 3×3陣列生成模塊

3×3陣列生成模塊利用了3個并行的24位移位寄存器,如果讀使能信號有效,則在每個時鐘的上升沿,將3個移位寄存器中的數(shù)據(jù)左移8位,然后將從3個雙口RAM中讀取的數(shù)據(jù)分別填充各自對應移位寄存器的后8位,在每個讀取周期內(nèi)循環(huán),直到讀使能信號置低時停止,然后等待下一行數(shù)據(jù)的循環(huán)。這樣,就生成了中值濾波所需要的3×3陣列。需要注意的是,每一幀圖像的第一行和最后一行因為沒有相應的上下行數(shù)據(jù),因此不能提取3×3陣列,所以需要控制信號將該兩行數(shù)據(jù)的3×3陣列剔除,以滿足圖像處理的準確性。

在雙口RAM的讀寫過程中,涉及到讀寫的時序問題,讀寫時序的控制必須滿足建立和保持時間的關(guān)系,以滿足圖像數(shù)據(jù)準確性的要求。在此,設計了一種新型的讀寫時序控制方法,首先,在數(shù)據(jù)傳輸至寫雙口RAM模塊時,利用一個與雙口RAM寫時鐘頻率相同,但是相位相差180°的時鐘做同步處理,使數(shù)據(jù)信號和控制信號的上升沿與該時鐘同步,然后,將同步后的數(shù)據(jù)信號和控制信號傳輸?shù)诫p口RAM的寫數(shù)據(jù)端口,則可以將觸發(fā)采集的寫時鐘的上升沿,恰好置于數(shù)據(jù)信號和控制信號的中央部分,以此保證數(shù)據(jù)寫入的穩(wěn)定性。該讀寫時序控制圖如圖5所示,其中,Clk_W為寫時鐘,Clk_180°為上文所講的同步時鐘,Data_in為同步前數(shù)據(jù)信號,Data_in1為同步后數(shù)據(jù)信號,由圖可以清楚的顯示,利用這種方法,可以將數(shù)據(jù)信號穩(wěn)定的寫入雙口RAM中,減少了時序設計時的計算時間,并且可以節(jié)約時序仿真的步驟,大大節(jié)省了開發(fā)時間。

圖3時序同步示意圖

熱成像儀相關(guān)文章:熱成像儀原理

評論