【從零開始走進(jìn)FPGA】 玩轉(zhuǎn)VGA

一、VGA的誘惑

本文引用地址:http://www.104case.com/article/275552.htm首先,VGA的驅(qū)動(dòng),這事,一般的單片機(jī)是辦不到的;由于FPGA的速度,以及并行的優(yōu)勢(shì),加上可現(xiàn)場配置的優(yōu)勢(shì),VGA的配置,只有俺們FPGA可以勝任,也只有FPGA可以隨心所欲地配置(當(dāng)然ARM也可以,應(yīng)用比較高吧)。

初學(xué)者就是喜歡看炫的效果,往往會(huì)忍不住想玩。尤其玩FPGA的,沒玩VGA就感到跟單片機(jī)沒啥提升,因此VGA的驅(qū)動(dòng)也不得不講。Bingo當(dāng)年也是如此。擋不住VGA的誘惑,初學(xué)者問Bingo VGA問題的人也是灰常的多,也許一般教科書理論太強(qiáng),實(shí)際應(yīng)用不是很身后,在此Bingo用淺顯易懂的語言來講述VGA的驅(qū)動(dòng)原理,以及通過設(shè)計(jì)一個(gè)可移植模塊的應(yīng)用來講述。

二、VGA驅(qū)動(dòng)原理

此處Bingo不參考任何資料,用當(dāng)年已學(xué)的知識(shí),用淺顯易懂的語言講述。

1、VGA接口

最主要的幾根線:

更詳細(xì)的資料,請(qǐng)看 http://baike.baidu.com/view/10346.htm

2、VGA時(shí)序

VGA其實(shí)就是相當(dāng)于一塊芯片,跟單片機(jī)驅(qū)動(dòng)IC一樣,滿足一定的時(shí)序,便能驅(qū)動(dòng)起來。

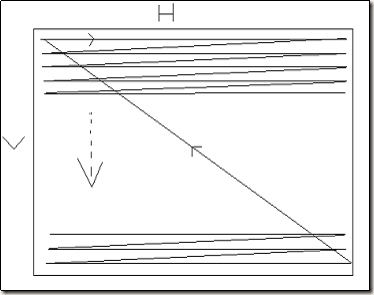

(1)掃描軌跡

VGA的掃描其實(shí)很簡單,大致軌跡如下所示:

沒掃描完一行,從新開始下一行;每掃完一場,重新開始下一場。相信你應(yīng)該看的懂。

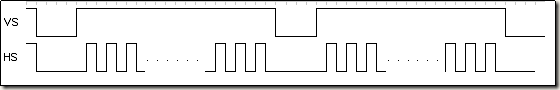

(2)行場掃描

以下是行掃描,場掃描HS,VS時(shí)序圖

如上如所示:VGA一直在掃描,沒一場的掃描包括了若干行掃描,如此循環(huán)。

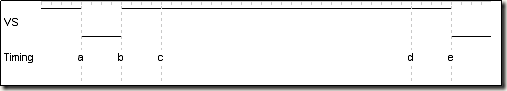

(3)VS時(shí)序深入分析

VS時(shí)序如下所示:

可見時(shí)序的循環(huán),可被劃分為a,b,c,d4個(gè)時(shí)期。這四個(gè)時(shí)期定義如下:

A~B:場消隱期 即同步,相當(dāng)于還原掃描坐標(biāo)吧

B~C:場消隱后肩 相當(dāng)于準(zhǔn)備開始掃描吧

C~D:場顯示期 掃描中,數(shù)據(jù)有效區(qū)域

D~E:場消隱前肩 完成掃描,相當(dāng)于準(zhǔn)備同步

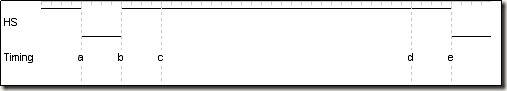

(4)HS時(shí)序深入分析

可見時(shí)序的循環(huán),可被劃分為a,b,c,d4個(gè)時(shí)期。這四個(gè)時(shí)期定義如下:

A~B:行消隱期 即同步,相當(dāng)于還原掃描坐標(biāo)吧

B~C:行消隱后肩 相當(dāng)于準(zhǔn)備開始掃描吧

C~D:行顯示期 掃描中,數(shù)據(jù)有效區(qū)域

D~E:行消隱前肩 完成掃描,相當(dāng)于準(zhǔn)備同步

綜上描述,我們只要知道每個(gè)時(shí)期的時(shí)間,便可以表示出VGA的時(shí)序。而FPGA的工作是由固定頻率的時(shí)鐘觸發(fā)的,因此某固定時(shí)間可以用n次觸發(fā)來表示。因此我們很容易就想到了FPGA常用的計(jì)數(shù)方法:比如說行掃描,我們計(jì)數(shù)0~H_total-1。用另一個(gè)進(jìn)程將其劃分為4個(gè)時(shí)期,安標(biāo)注分配。其實(shí)這相當(dāng)于狀態(tài)機(jī)。

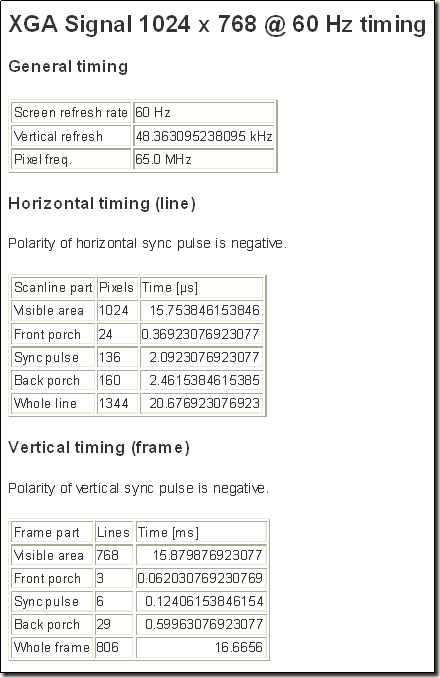

以下是固定分辨率1024*768 60fps下HS,VS的標(biāo)準(zhǔn):

用代碼表示4個(gè)時(shí)期,如下:

// VGA_1024_768_60fps_65MHz

// Horizontal Parameter( Pixel )

parameter H_DISP = 11'd1024,

parameter H_FRONT = 11'd24,

parameter H_SYNC = 11'd136,

parameter H_BACK = 11'd160,

parameter H_TOTAL = 11'd1344,

// Virtical Parameter( Line )

parameter V_DISP = 10'd768,

parameter V_FRONT = 10'd3,

parameter V_SYNC = 10'd6,

parameter V_BACK = 10'd29,

parameter V_TOTAL = 10'd806

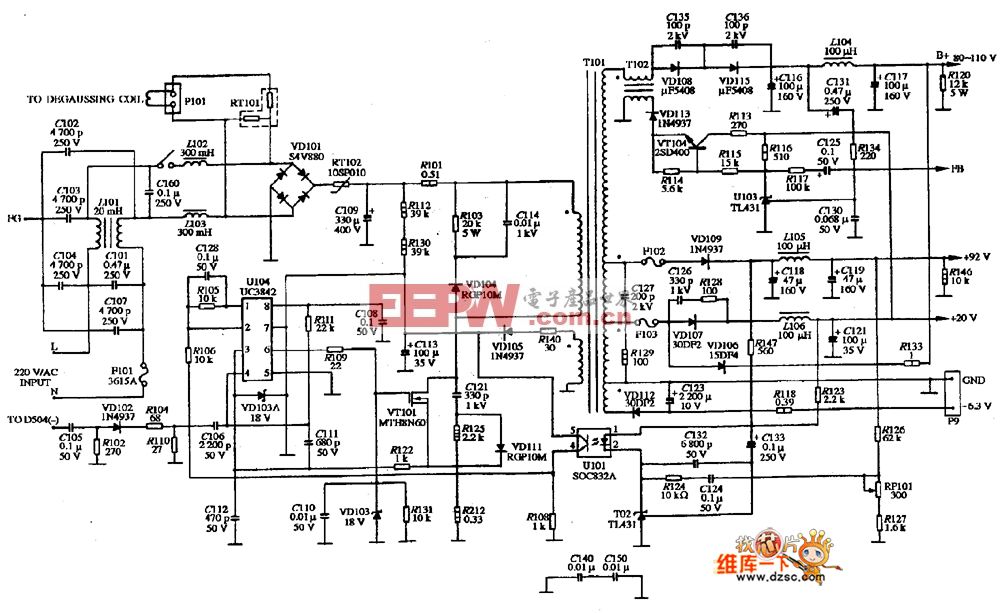

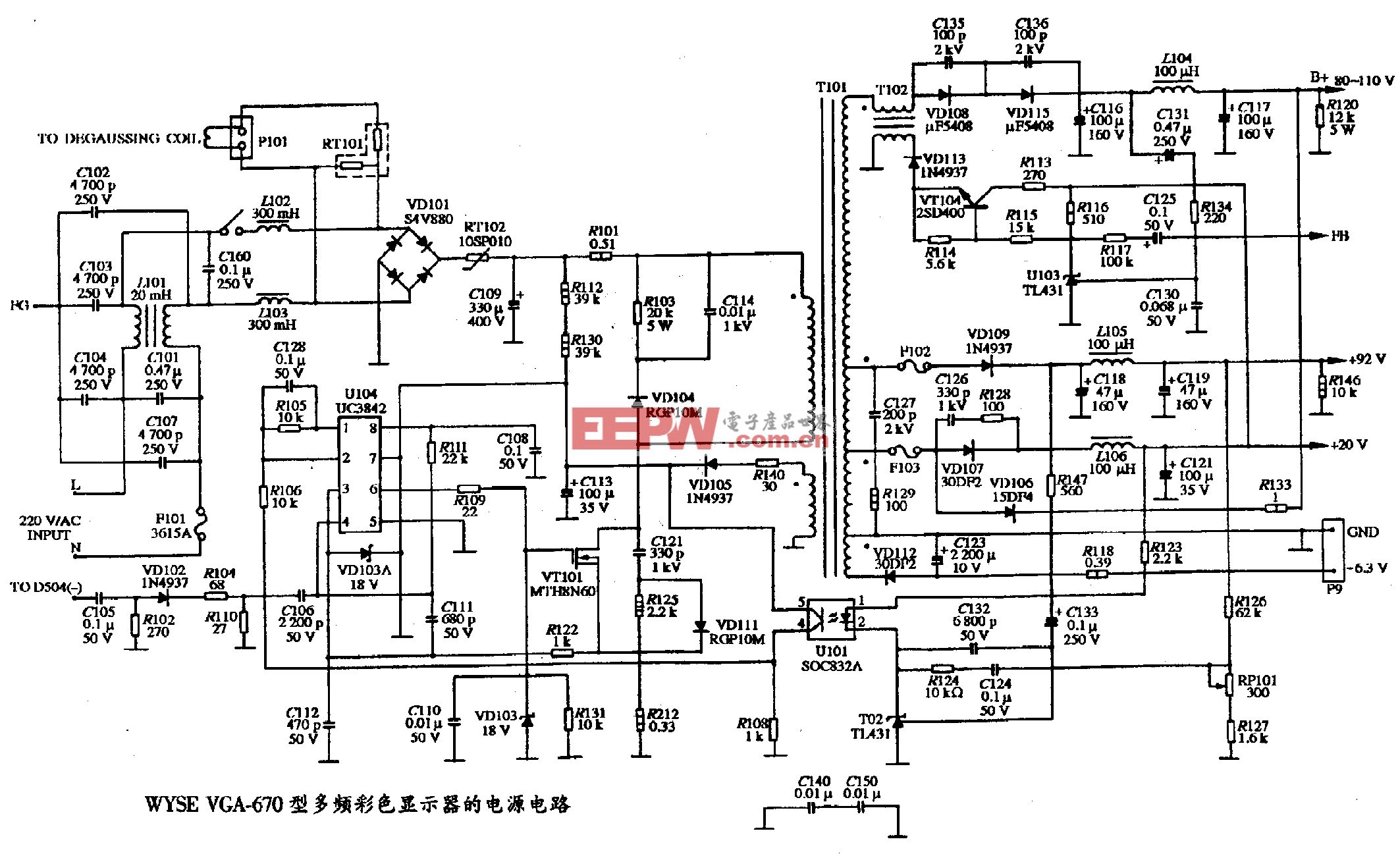

3、VGA電路

(1)三原色

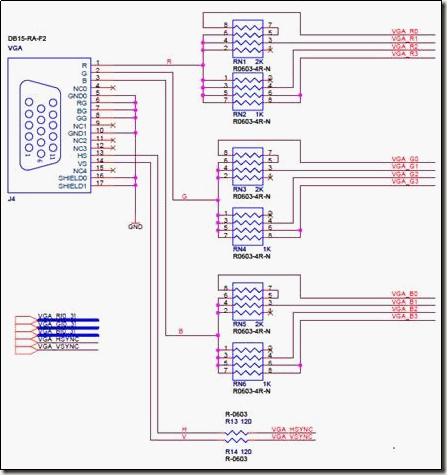

VGA接口:R,G,B三通道,直接賦給數(shù)字信號(hào),RGB,最多產(chǎn)生8種色彩。這是最基本的。電路如下所示:

(2)真彩顯示

a) 電阻網(wǎng)絡(luò)

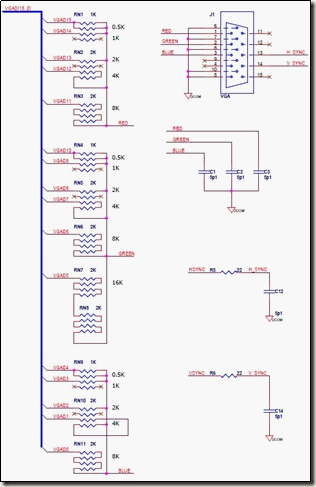

考慮到成本意識(shí)實(shí)現(xiàn)的簡易方案,用R-2R電阻網(wǎng)絡(luò)分流模擬DAC替換ADV7123視頻轉(zhuǎn)換芯片。見以下幾個(gè)方案:

DE1 VGA模擬電路

小馬哥電路圖

具體設(shè)計(jì)參考Bingo當(dāng)年總結(jié):

http://www.cnblogs.com/crazybingo/archive/2010/07/31/1789323.html

或者參考小馬哥設(shè)計(jì):

http://www.ourdev.cn/bbs/bbs_content.jsp?bbs_sn=3582675&bbs_page_no=1&search_mode=2&search_text=VGA&bbs_id=9999

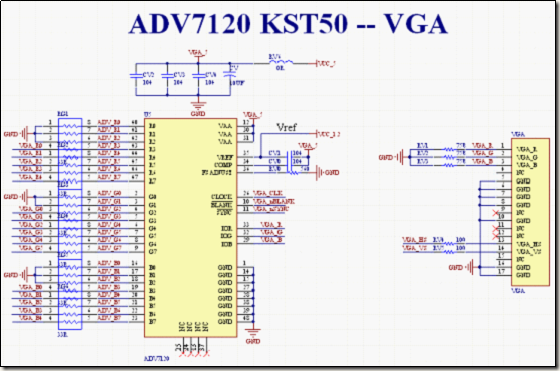

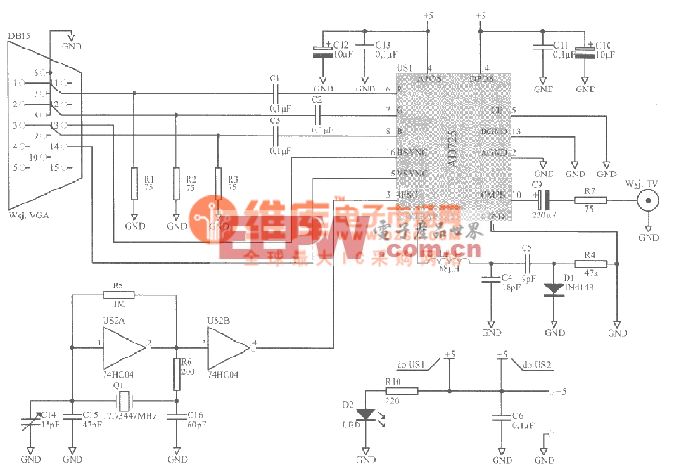

b) 專用視頻轉(zhuǎn)換芯片

利用專用視頻轉(zhuǎn)換芯片,ADV7120等,將數(shù)字信號(hào)轉(zhuǎn)換為VGA RGB的模擬信號(hào)。ADV7120為高速D/A芯片,將數(shù)字信號(hào)轉(zhuǎn)換為模擬信號(hào)輸給VGA,電路如下:

三、可移植VGA模塊設(shè)計(jì)

Bingo玩VGA也算是比較早了,當(dāng)年也是視覺的誘惑,以及唯FPGA獨(dú)尊的優(yōu)勢(shì)。于是之后一發(fā)而不可收拾。本章Bingo將自己這些年最終優(yōu)化的VGA驅(qū)動(dòng)模塊,發(fā)布至此。本模塊所有代碼均Bingo獨(dú)家創(chuàng)造,請(qǐng)尊重版權(quán)哈。

本設(shè)計(jì)已經(jīng)封裝成模塊,只要修改時(shí)序參數(shù)、掃描時(shí)鐘參數(shù)以及在vga_display.v中添加顯示電路,即可。方便移植,希望對(duì)大家有用。

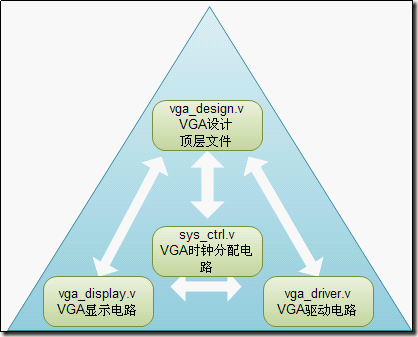

1、模塊劃分

(1)vga_design.v

工程頂層文件,例化各個(gè)模塊。

(2)sys_ctrl.v

PLL時(shí)鐘分配電路。

(3)vga_display.v

顯示電路,根據(jù)時(shí)序,用于描述VGA的顯示電路。

(4)vga_driver.v

VGA驅(qū)動(dòng)電路,對(duì)時(shí)序,狀態(tài)的約束。

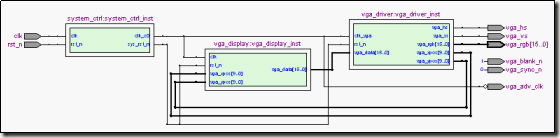

RTL圖如下所示:

fpga相關(guān)文章:fpga是什么

評(píng)論