- 摘要:針對調制樣式在不同環境下的變化,采用了FPGA部分動態可重構的新方法,通過對不同調制樣式信號的解調模塊的動態加載,來實現了不同環境下針對不同調制樣式的解調這種方式比傳統的設計方式具有更高的靈活性、可

- 關鍵字:

FPGA 部分動態可重構 信號解調系統

- 摘要:為了解決傳統的光伏測試儀功能單一,只能夠測量光伏電池基本參數的問題,采用了增加采樣信道,由FPGA控制采樣模式的方法,設計完成了一款雙模式的光伏電池測試儀。在完成光伏電池I-V曲線等參數測量的同時可以實

- 關鍵字:

FPGA 雙模式 光伏電池 測試儀

- MP3數字播放機系統的FPGA設計介紹,1 引 言

MPEG(活動影像專業人員組織)是為數字音頻確定單一編碼和解碼(壓縮/解壓縮)方法于1988年建立的。1992年,國際標準組織(ISO)和國際電工委員會(IEC)為音頻和視頻編碼建立了MPEG1(ISO/IEC11172)標準

- 關鍵字:

設計 介紹 FPGA 系統 數字 播放機 MP3

- FPGA時序收斂分析,您編寫的代碼是不是雖然在仿真器中表現正常,但是在現場卻斷斷續續出錯?要不然就是有可能在您使用更高版本的工具鏈進行編譯時,它開始出錯。您檢查自己的測試平臺,并確認測試已經做到 100% 的完全覆蓋,而且所有測試

- 關鍵字:

分析 收斂 時序 FPGA

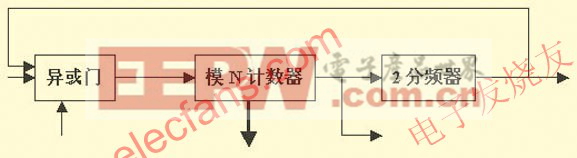

- 基于VHDL和FPGA的多種分頻實現方法介紹,分頻器是數字系統設計中的基本電路,根據不同設計的需要,我們會遇到偶數分頻、奇數分頻、半整數分頻等,有時要求等占空比,有時要求非等占空比。在同一個設計中有時要求多種形式的分頻。通常由計數器或計數器的級聯

- 關鍵字:

方法 介紹 實現 多種 VHDL FPGA 基于

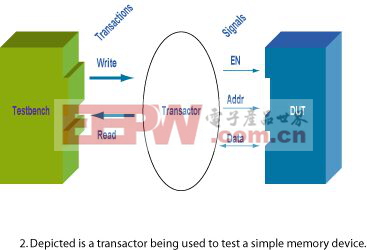

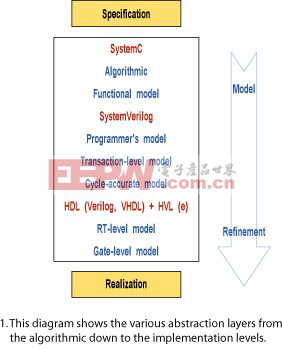

- 如何在SoC設計中使用事務處理(二),建模、驗證與調試需要統一標準的符號和框架,以便使架構師和設計工程師能夠協同進行復雜SoC的開發。事務處理級模型(TLM)是進行這種分析的理想模型,在片上系統(SoC)設計中使用事務處理級建模,可讓設計從高效率協同仿

- 關鍵字:

事務 處理 使用 設計 SoC 如何

- 如何在SoC設計中使用事務處理(一), 建模、驗證與調試需要統一標準的符號和框架,以便使架構師和設計工程師能夠協同進行復雜SoC的開發。事務處理級模型(TLM)是進行這種分析的理想模型,在片上系統(SoC)設計中使用事務處理級建模,可讓設計從高效率協同

- 關鍵字:

事務 處理 使用 設計 SoC 如何

- 隨著 10Gb 以太網發展趨于成熟,且業界甚至已開始期待 40GbE 和 100GbE 以太網的出現,新一代網絡基礎架構方興未艾。融合型網絡在流量處理方面向可擴展開放式平臺提出了全新的挑戰。新一代融合型基礎設施底板通常由高

- 關鍵字:

FPGA 賽靈思

- 有多個處理單元的SoC器件目前是產品設計鏈上的重要一環。本文綜合各種因素評估了不同處理單元的優缺點,并通過衛星無線電接收器的設計實例幫助開發人員理解SoC所涉及處理任務之間的復雜平衡并有效掌握系統功能的劃分

- 關鍵字:

SoC 處理單元 性能

- 提起FPGA,我們首先想到的是美國的三大公司,在這個領域,除了美國之外,全球其他國家基本沒有話語權。但是從今以后,有一家代表中國FPGA產業的公司要這個舞臺上一展舞姿,請記住她的名字:京微雅格(Capital Microelectronics)。京微雅格公司CEO劉明博士比喻京微雅格在FPGA產業中的位置:我們已經加入到這個俱樂部,成為其中的一員。

- 關鍵字:

京微雅格 FPGA

- 摘要:二維離散余弦(DCT)在H.264視頻編碼中承擔者信號從時域到頻域變換的作用。在現場可編程邏輯門陣列(FPGA)上設計了高效的采用流水線結構的H.264 DCT硬件電路。首先,把二維4times;4 DCT變換轉換成二次一維DCT變

- 關鍵字:

FPGA 264 DCT 算法

- 使用EP2C35 FPGA 設計了多個串口工作,出現了幾個問題. 第一次, 由于內核電源1.2V 供電不是完整平面,而是帶狀線供電,EP2C35 在代碼容量大的情況下,而且輸入FPGA 信號變換頻繁, 造成整個EP2C35 所有的D觸發器停止翻轉.

- 關鍵字:

FPGA 線路 尖峰 毛刺

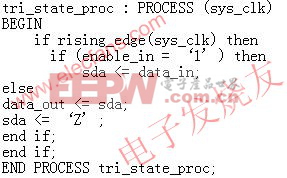

- INOUT引腳:1.FPGA IO在做輸入時,可以用作高阻態,這就是所說的高阻輸入;2.FPGA IO在做輸出時,則可以直接用來輸入輸出。芯片外部引腳很多都使用inout類型的,為的是節省管腿。就是一個端口同時做輸入和輸出。 ino

- 關鍵字:

inout FPGA 端口 方法

- 上文中說到了CycloneIV中的幾種配置方式,JTAG或者AS模式配置EPCS64,其中我個人比較傾向于將上文提到的統稱為串行配置模式,而EPCS系列的配置芯片都是屬于串行配置芯片。而在本文中講到StratixIII的配置所使用的是F

- 關鍵字:

StratixIII CycloneIV FPGA 開發板

fpga soc介紹

您好,目前還沒有人創建詞條fpga soc!

歡迎您創建該詞條,闡述對fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473