如何在SoC設(shè)計中使用事務(wù)處理(一)

建模、驗證與調(diào)試需要統(tǒng)一標(biāo)準(zhǔn)的符號和框架,以便使架構(gòu)師和設(shè)計工程師能夠協(xié)同進(jìn)行復(fù)雜SoC的開發(fā)。事務(wù)處理級模型(TLM)是進(jìn)行這種分析的理想模型,在片上系統(tǒng)(SoC)設(shè)計中使用事務(wù)處理級建模,可讓設(shè)計從高效率協(xié)同仿真和高產(chǎn)出的分析與調(diào)試中受益。

本文引用地址:http://www.104case.com/article/148680.htm 片上系統(tǒng)(SoC)平臺是異質(zhì)性的實體。它們通常包含至少一個處理器部件(譬如微處理器或DSP),以及外圍設(shè)備、隨機(jī)邏輯、嵌入式存儲器、通訊基礎(chǔ)結(jié)構(gòu)和傳感器、傳動裝置之類的外部接口元件。這些變化多樣的設(shè)計平臺正在將設(shè)計焦點(diǎn)和折衷分析轉(zhuǎn)移至通訊層面。

由 于SoC內(nèi)的功能單元常常是通過若干標(biāo)準(zhǔn)及基于數(shù)據(jù)總線的專有協(xié)議來實現(xiàn)通信,所以理解模塊間通訊已經(jīng)成為驗證的一個關(guān)鍵。設(shè)計活動向通訊基礎(chǔ)架構(gòu)設(shè)計的 轉(zhuǎn)移,也促進(jìn)了對混合級建模以及調(diào)試技術(shù)的使用。這些技術(shù)使設(shè)計工程師能夠完全應(yīng)對從電阻晶體管邏輯電路(RTL)到更高事務(wù)處理級的轉(zhuǎn)移,而且無需中斷 使用目前的功能驗證方法。

有鑒于現(xiàn)今協(xié)議的復(fù)雜性,要詳盡理解信號級上的同步互動是艱難而又費(fèi)時的。此外,由于不同的團(tuán)隊和個人都將設(shè)計視為從規(guī)格到實現(xiàn)的提煉過程,所以各個設(shè)計團(tuán)隊之間以及團(tuán)隊內(nèi)部都需要找到一個通用參考框架(frame)。

有代表性的參考標(biāo)準(zhǔn)必須足夠靈活以便適合于多個應(yīng)用領(lǐng)域。它也必須經(jīng)得起抽象和提煉,以便適用于由上而下設(shè)計或由下而上的配置。事務(wù)處理級建模(TLM)被用作所需的中間建模抽象級,成為連接頂層和底層的橋梁。

事務(wù)處理級建模的概念

目前的SoC設(shè)計流程是一個混合過程,包括由上而下的從規(guī)格制定到實現(xiàn)、從下而上的設(shè)計模塊集成,以及對來自外部供應(yīng)商或內(nèi)部重用模塊的知識產(chǎn)權(quán)的驗證。事 務(wù)處理可以作為連接不同設(shè)計建模層間間隙的一個最終優(yōu)化規(guī)范。這包括用高級語言實現(xiàn)的無時序(untimed)純功能性建模、通過架構(gòu)估計得到大致時序的 功能級,一直到實現(xiàn)級、循環(huán)精確的RTL。

除此之外,事務(wù)處理級建模也作為系統(tǒng)工程師和專用模塊開發(fā)者之間的一個通用描述性媒介而發(fā)揮著 作用,該媒介超越了不同的適用于具體設(shè)計或驗證活動的語言的界限。于是,事務(wù)處理就變成實施構(gòu)架開發(fā)和折衷分析的一種形式。它是一種通過分析系統(tǒng)功能有效 性和性能度量(譬如整體吞吐量、模塊與存儲器交互延遲等)來自動進(jìn)行設(shè)計理解和調(diào)試過程的手段。

|

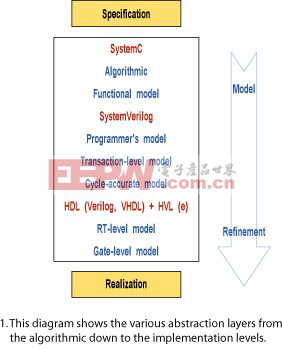

圖1顯示的是從算法級到實現(xiàn)級的各個抽象級,通常包括SystemC(IEEE P1666)、SystemVerilog(IEEE P1800)和e(IEEE P1647)在內(nèi)的幾種功能建模與驗證語言(及標(biāo)準(zhǔn))被用于設(shè)計。另外,先進(jìn)的方法實踐,例如從OpenVera的“參考驗證法指南”以及e的“e再使用法推薦”抽取出的方法實踐,為算法、構(gòu)架以及事務(wù)處理級建模提供參考。

事務(wù)處理級建模是一個相當(dāng)普通的應(yīng)用,它涉及并描述設(shè)計的每一個功能線程。事務(wù)處理級的焦點(diǎn)是“如何”進(jìn)行,特別是通訊交互“如何”進(jìn)行,而不在于功能是 “什么”。事務(wù)處理所提供的是執(zhí)行細(xì)節(jié)在時間上的抽象與空間上的封裝在DD這是最初注重通訊基礎(chǔ)架構(gòu)而不是功能模塊的思想的體現(xiàn)。做這樣的抽象建模的好處 是驗證效率高。事實上,對事務(wù)處理的運(yùn)用正變得日益廣泛、多種多樣,并成為主流。

在模塊間捕捉同步傳輸?shù)氖聞?wù)處理也注定會成為折衷分析中的重要角色。因此,建模與記錄事務(wù)處理對提升基于事務(wù)處理的驗證和調(diào)試技術(shù)非常關(guān)鍵,而驗證和調(diào)試技術(shù)是提高開發(fā)效率與設(shè)計質(zhì)量所必須的。

如何進(jìn)行事務(wù)處理級建模

高級語言(也稱為“HLL”,例如SystemC)、其它的硬件驗證語言(也稱為“HVL”,例如OpenVera、e)以及測試向量(testbenchz)與硬件設(shè)計語言(例如SystemVerilog)對事務(wù)處理都有程度不一的內(nèi)在支持。SystemC (www.SystemC.org)可為建模語言內(nèi)置的用戶驅(qū)動事務(wù)處理的創(chuàng)建提供支持,并可把它們記錄到數(shù)據(jù)庫中,就如同采用SCV函數(shù)庫的sc_trace()寫入數(shù)據(jù)庫一樣。SCV有許多預(yù)先定義的非常有用的類,包括下面三個主要的記錄對象:scv_tr_db: 事務(wù)處理數(shù)據(jù)庫對象,它允許用戶控制記錄。該對象是通用的且獨(dú)立于數(shù)據(jù)庫格式。第三方記錄API供應(yīng)商可以將底層服務(wù)對應(yīng)到他們自己的數(shù)據(jù)庫方案中。

評論