支持下一代 SoC 和存儲(chǔ)器的工藝創(chuàng)新

本文將解析使 3D NAND、高級(jí) DRAM 和 5nm SoC 成為可能的架構(gòu)、工具和材料。

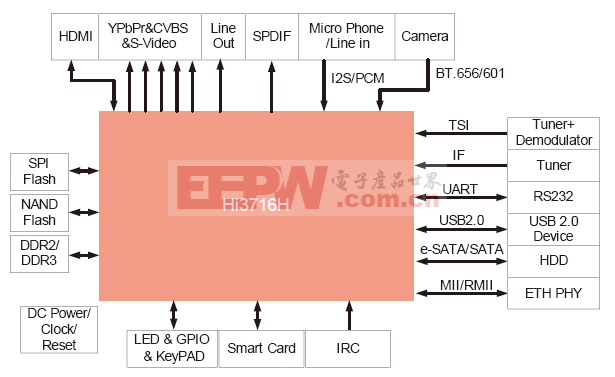

要提高高級(jí) SoC 和封裝(用于移動(dòng)應(yīng)用程序、數(shù)據(jù)中心和人工智能)的性能,就需要對(duì)架構(gòu)、材料和核心制造流程進(jìn)行復(fù)雜且代價(jià)高昂的更改。

本文引用地址:http://www.104case.com/article/202302/443794.htm正在考慮的選項(xiàng)包括新的計(jì)算架構(gòu)、不同的材料,包括更薄的勢(shì)壘層和熱預(yù)算更高的材料,以及更高縱橫比的蝕刻和更快的外延層生長(zhǎng)。挑戰(zhàn)在于如何以不偏離功率、性能和面積/成本 (PPAC) 曲線太遠(yuǎn)的方式組合這些。

當(dāng)今的頂級(jí)智能手機(jī)使用集成多種低功耗、高性能功能的移動(dòng) SoC 平臺(tái),包括一個(gè)或多個(gè) CPU 內(nèi)核、GPU、AI 引擎、DSP 和其他外形緊湊的設(shè)備。例如,高通新的驍龍 888 5G 平臺(tái)采用三星的 5 納米 finFET 技術(shù)制造,最近通過(guò)工藝改進(jìn)和設(shè)計(jì)技術(shù)協(xié)同優(yōu)化針對(duì) CPU 性能和高良率進(jìn)行了優(yōu)化。

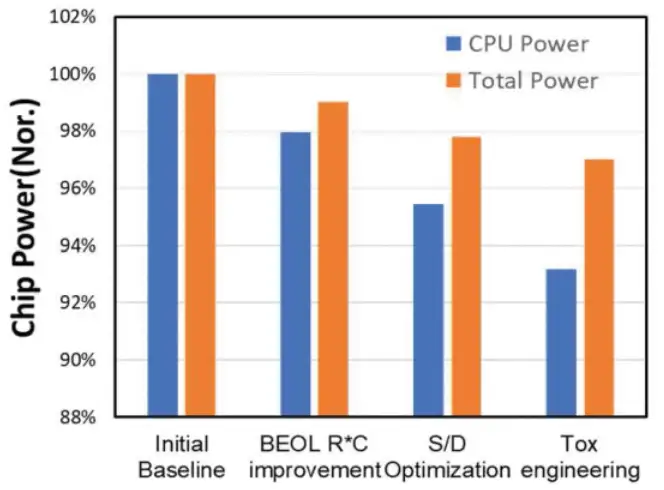

圖 1:FEOL 源極/漏極和柵極氧化物厚度優(yōu)化以及互連 RC 改進(jìn)降低了器件功耗。來(lái)源:高通/IEEE IEDM

將工作芯片拿出來(lái)是一項(xiàng)挑戰(zhàn)。美光團(tuán)隊(duì)表示,鰭間距、柵極間距和金屬間距以及 SRAM 單元面積的激進(jìn)尺寸縮放最初導(dǎo)致了多個(gè)工藝熱點(diǎn)。減輕最重要的系統(tǒng)缺陷需要接觸、柵極和外延協(xié)同優(yōu)化。Metal-1 到 Metal-2 的空隙通過(guò) OPC 調(diào)整和嚴(yán)格的在線過(guò)程控制得到解決。「與初始基線相比,低壓操作模式下的良率損失減少了 5 倍,對(duì)多個(gè)模塊進(jìn)行了測(cè)試和工藝集成優(yōu)化,包括間隔/襯墊優(yōu)化、器件 Vt 居中、新的 OPC 掩模和更換金屬柵極 (RMG) 清潔,」他們?cè)谧罱?IEDM 會(huì)議上發(fā)表的一篇論文中寫道。「設(shè)計(jì)和 DFT 修改有效地減少了更嚴(yán)格的 V min 的電阻故障低壓配電。」

動(dòng)態(tài)電壓篩選和極低電壓存儲(chǔ)器修復(fù)有助于消除異常值,增加規(guī)格余量。5nm CPU 在與 7nm 設(shè)備相同的功耗下實(shí)現(xiàn)了 10% 以上的性能提升,或者在相同速度下功耗降低了 15%。

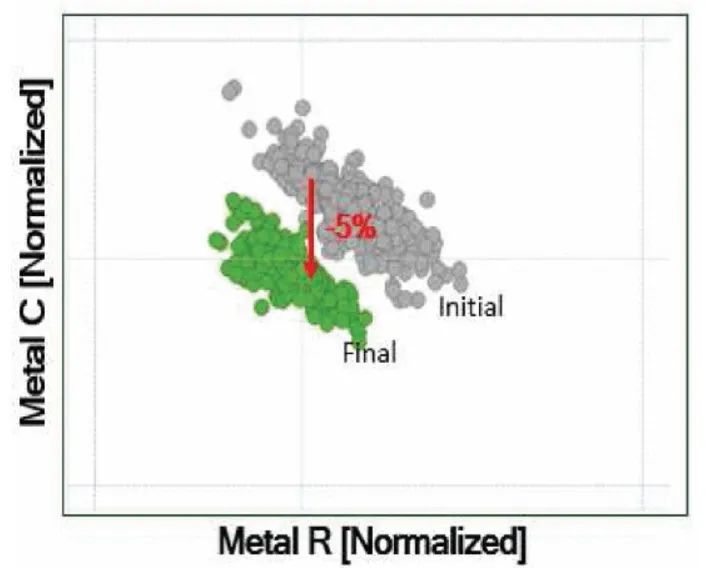

為了支持全天的電池壽命,通過(guò)外延層前端源極和漏極調(diào)整以及柵極氧化物工程解決了總功率問(wèn)題。在鰭片、多晶硅、源極/漏極和 RMG 模塊的幾個(gè)工藝步驟中進(jìn)行了晶圓內(nèi)工藝負(fù)載改進(jìn)(見(jiàn)圖 1)。通過(guò)最小化阻擋層的影響、創(chuàng)建具有統(tǒng)一高度的通孔和優(yōu)化蝕刻停止(參見(jiàn)圖 2),中間線和 BEOL 互連針對(duì)較低的 RC 進(jìn)行了優(yōu)化。美光團(tuán)隊(duì)補(bǔ)充說(shuō),第二年的工藝改進(jìn)提供了功率性能優(yōu)勢(shì),包括通過(guò)進(jìn)一步的柵極優(yōu)化、FEOL 蓋層減少和 MOL 電阻降低使用相同設(shè)計(jì)提高 5% 的速度。

圖 2:阻擋層、通孔高度和蝕刻停止層的調(diào)整將 RC 常數(shù)降低了 5%。來(lái)源:高通/IEEE IEDM

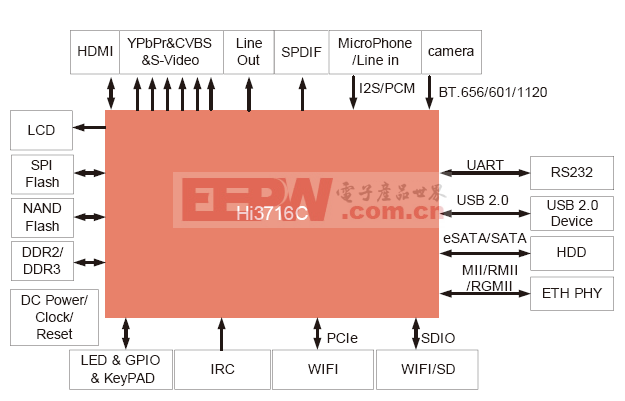

擴(kuò)展 3D NAND

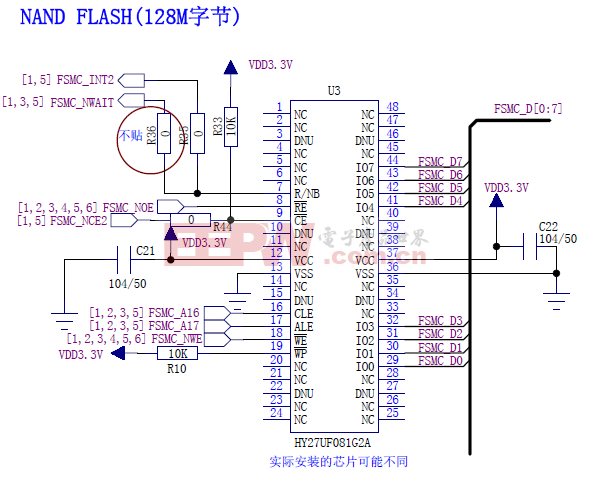

3D NAND 現(xiàn)在在 PC、移動(dòng)設(shè)備和數(shù)據(jù)中心中無(wú)處不在,并且正在迅速進(jìn)入汽車和神經(jīng)網(wǎng)絡(luò)應(yīng)用。3D 配置中的電荷捕獲閃存 (CTF) 通過(guò)堆疊字線、使用大量沉積、蝕刻、填充和退火步驟以及更少的光刻圖案化步驟(相對(duì)于邏輯)以低成本擴(kuò)展。位密度每年大幅增加 30%。

為了顯著減小裸片尺寸,所有領(lǐng)先的 NAND 制造商都開(kāi)始在存儲(chǔ)器陣列下方制造 CMOS 外圍電路。三星率先在 2010 年左右將其外圍單元 (COP) V-NAND 推向市場(chǎng),顯著縮小了裸片尺寸。但增加位密度背后的持續(xù)縮放引擎是重復(fù)的層堆棧——使用多個(gè)沉積步驟、高縱橫比蝕刻和高 AR 填充能力來(lái)加速陣列(層)中存儲(chǔ)字線的數(shù)量。三星、美光和海力士的這些層數(shù)超過(guò) 200,它們都制定了到 2030 年達(dá)到 1000 層的路線圖。

Russ Meyer 和 Micron 的同事在最近的 IEDM 上討論了幾個(gè)可以進(jìn)一步提高 NAND 位密度和性能的旋鈕,包括替代塊架構(gòu)、新的單元薄膜和間距縮放選項(xiàng)。「3D NAND 繼續(xù)提供甚至加速數(shù)據(jù)行業(yè)所需的 NAND 縮放趨勢(shì),部分原因是其更大的柵極面積和改進(jìn)的環(huán)柵 (GAA) 架構(gòu)的靜電。」 繼續(xù)沿著這條道路前進(jìn),將在未來(lái) 5 到 6 年內(nèi)實(shí)現(xiàn) 1000 層,芯片厚度接近 100μm,這對(duì)許多應(yīng)用來(lái)說(shuō)是無(wú)法接受的。

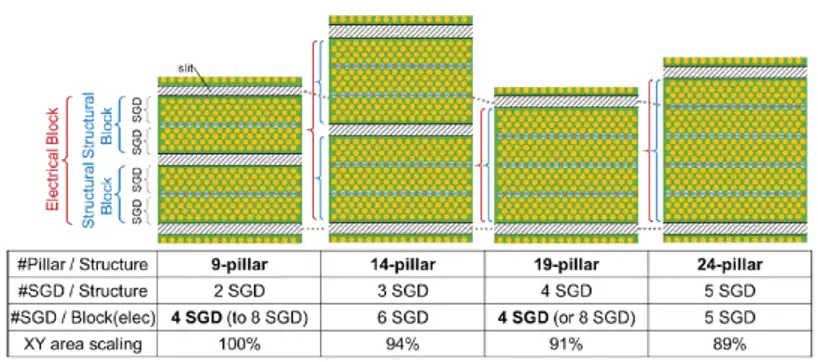

通過(guò)增加 50% 以上的 WL 層(字線充當(dāng)柵極并圍繞柱狀溝道),該結(jié)構(gòu)可能會(huì)出現(xiàn)擺動(dòng)和不穩(wěn)定。這反過(guò)來(lái)又會(huì)導(dǎo)致諸如字線泄漏、單元形成問(wèn)題和位線接觸未對(duì)準(zhǔn)之類的故障。美光正在探索的一種策略是將 9 柱塊更改為 19 柱塊,其結(jié)構(gòu)寬度約為 2 倍,并且與多家制造商使用的當(dāng)前 4 柱選擇門(子塊)的塊架構(gòu)兼容(見(jiàn)圖 3)。這一變化使單元面積減少了 9%。

圖 3:例如,與從傳統(tǒng)的 9 柱結(jié)構(gòu)(柱行/塊)到 19 柱的變化相關(guān)的 NAND 陣列縮放可使塊縮小 9%,這與 4 柱子塊兼容。來(lái)源:美光/IEEE IEDM

XY 縮放在平面 NAND 中遇到了極限,而 3D NAND 正在接近它。其他問(wèn)題包括由電池間耦合(即噪聲)引起的器件退化。第一步,WL 柵極替換,對(duì)于 19 柱更寬的塊架構(gòu)變得更具挑戰(zhàn)性。犧牲層去除和 WL 金屬填充的縱橫比較大,導(dǎo)致較差的金屬臺(tái)階覆蓋(和較高的 WL 電阻),以及空隙和接縫中的污染。該小組發(fā)現(xiàn),更薄的替代阻擋層金屬可以更好地防止雜質(zhì),從而降低塊狀鎢填充物的電阻率。

陣列高度的增加也可以通過(guò)單元間距縮放來(lái)減輕,使柱之間的間距。蝕刻縱橫比確實(shí)隨著間距的縮小而適度增加,但更大的問(wèn)題是在減小的通道寬度下對(duì)讀取性能的影響。需要新的集成方案。

美光團(tuán)隊(duì)進(jìn)一步表示,未來(lái)的 NAND 每個(gè)單元可以包含超過(guò) 4 位。然而,相對(duì)于體積位密度的增加,每個(gè)單元更多的位會(huì)導(dǎo)致每個(gè)狀態(tài)的電子數(shù)量損失更大。「首先將電池設(shè)備的尺寸(例如,最好是柱間距 XY 縮放)縮放到工藝能力的極限更為合理。創(chuàng)新的模塊架構(gòu)和 WL 驅(qū)動(dòng)程序方案是未來(lái)節(jié)點(diǎn)的 3D NAND 性能可擴(kuò)展性的關(guān)鍵,」他們總結(jié)道。

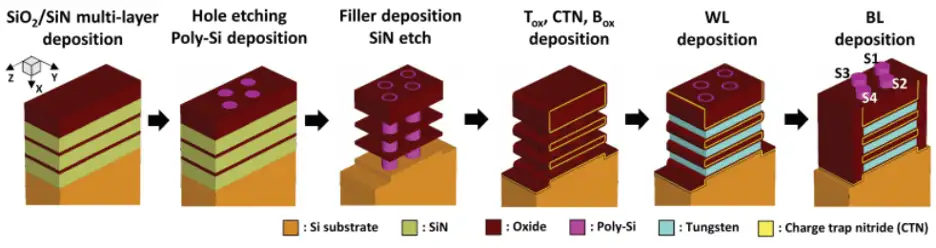

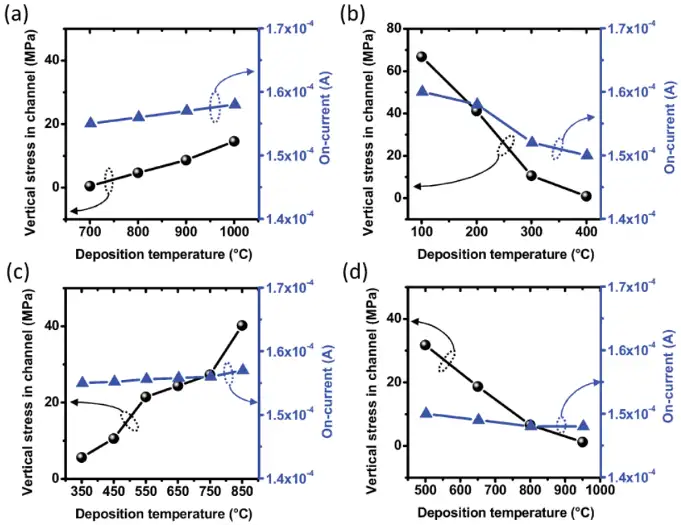

隨著公司繼續(xù)擴(kuò)展 3D NAND,他們正在觀察 3D 閃存結(jié)構(gòu)中的應(yīng)力分布與電氣性能之間的關(guān)系。正如浦項(xiàng)科技大學(xué)和三星的論文所述,這些結(jié)構(gòu)由隧道氧化物、電荷捕獲氮化物、鎢和多晶硅通道組成,因此不同材料之間的晶格失配和熱失配會(huì)導(dǎo)致機(jī)械應(yīng)力(見(jiàn)圖 4)。熱退火確實(shí)會(huì)導(dǎo)致一些松弛,但這些日益受限的 3D NAND 結(jié)構(gòu)中的凈機(jī)械應(yīng)力仍然會(huì)對(duì)電氣性能產(chǎn)生很大影響。

圖 4:多重沉積、高縱橫比蝕刻和填充步驟創(chuàng)建電荷捕獲 NAND 堆疊。來(lái)源:IEEE J. EDS

有趣的是,模擬確定降低鎢的沉積溫度具有最顯著的影響,因?yàn)殒u施加的應(yīng)力遠(yuǎn)遠(yuǎn)超過(guò)其他薄膜施加的應(yīng)力,并且對(duì)溝道應(yīng)力的影響最大(見(jiàn)圖 5)。通過(guò)降低鎢沉積溫度(和應(yīng)力),多晶硅溝道的導(dǎo)帶和價(jià)帶移動(dòng),有效地提高了性能。

圖 5:多晶硅 (a)、鎢 (b)、氧化層 (c) 和電荷陷阱氮化物 (d) 的平均溝道應(yīng)力與導(dǎo)通電流變化的關(guān)系。來(lái)源:IEEE J. EDS

研究人員強(qiáng)調(diào),相對(duì)于隧道氧化物 (SiO 2 ) 和多晶硅,電荷陷阱氮化物和鎢具有更高的 CTE(熱膨脹系數(shù))。提高鎢和氮化物沉積溫度可有效地誘導(dǎo)壓應(yīng)力并降低導(dǎo)通電流,而不會(huì)影響器件的存儲(chǔ)器工藝窗口和閾值電壓。進(jìn)一步的模擬表明,降低鎢沉積溫度是提高 NAND 性能的最佳手段。

有了所有這些窄的、高深寬比的孔,間隙填充成為 3D NAND 的關(guān)鍵需求也就不足為奇了——尤其是因?yàn)槌练e溫度在 300°C 到 900°C 范圍內(nèi)。最近開(kāi)發(fā)的一個(gè)例子是來(lái)自 Brewer Science 的旋涂碳材料,它已被用于填充 0.5 x 10μm 的溝槽,在 550°C 下熱處理 60 分鐘后沒(méi)有出現(xiàn)薄膜空洞、開(kāi)裂或分層的跡象。熱穩(wěn)定的旋涂碳表現(xiàn)出最小的收縮和質(zhì)量損失。旋涂后,它使用軟烘烤和熱板固化,然后根據(jù)需要進(jìn)行爐內(nèi)氮化。

為 AI、汽車擴(kuò)展 DRAM

機(jī)器學(xué)習(xí)和 AI 以及汽車領(lǐng)域的應(yīng)用快速增長(zhǎng),需要增加 DRAM 的帶寬。這些外圍電路執(zhí)行不同的功能(即行/列解碼器、讀出放大器、I/O 數(shù)據(jù)緩沖器),因此需要具有低柵極泄漏、關(guān)斷電流和高擊穿電壓以及 DRAM 工藝兼容性的優(yōu)化晶體管。即使對(duì)于多晶硅/氧化物平面 FET 也是如此。在使用高 k 金屬柵極的 finFET 晶體管中,必須優(yōu)化流程以承受長(zhǎng)時(shí)間的高溫退火(550°C 下 4 小時(shí))并保持電氣特性。

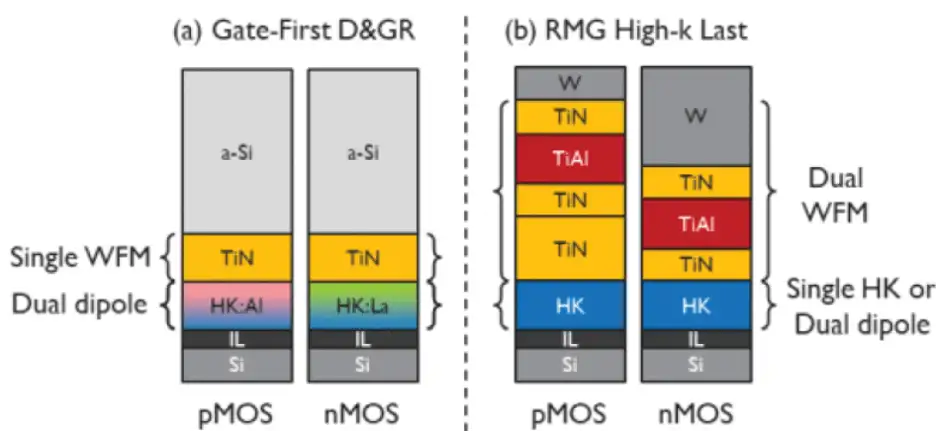

圖 6:與后柵極高 k 替代金屬柵極工藝(右)相比,先柵極擴(kuò)散和柵極置換(左)導(dǎo)致更高的閾值電壓和更少地用于功函數(shù)調(diào)整的金屬柵極選項(xiàng)。來(lái)源:imec/IEEE IEDM

imec 的 Elena Capogreco 及其同事最近展示了一種 14 納米高 k / 金屬柵極替換柵極方法,該方法可以在承受長(zhǎng)時(shí)間退火的同時(shí)實(shí)現(xiàn)低于 0.2V 的 nMOS 閾值電壓。「除了減少熱預(yù)算外,與柵極優(yōu)先擴(kuò)散和柵極替換方案(見(jiàn)圖 6)相比,使用 RMG 流程的另一個(gè)優(yōu)勢(shì)是增加了 nMOS 和 nMOS 之間 WFM(功函數(shù)金屬)工程的自由度。」

研究人員解釋說(shuō),雖然用于外圍 DRAM 電路的低成本 CMOS finFET 中的柵極優(yōu)先 HKMG 已經(jīng)實(shí)現(xiàn),但由于高溫退火引起的費(fèi)米能級(jí)引腳(特別是在 pMOS 器件上),閾值電壓相對(duì)較高。新的熱穩(wěn)定柵極堆疊包括 1nm 界面氧化物、1.9nm 氧化鉿、2nm TiN、5nm TiAl、3nm TiN 以及鎢 CVD 和 CMP。

目標(biāo)柵極長(zhǎng)度為 30nm。一些加工經(jīng)驗(yàn)教訓(xùn)包括需要用氮化硅覆蓋鎢以抑制退火引起的柵極氧化物退化。CMP 之后的氮化物覆蓋進(jìn)一步封裝了金屬。通過(guò)在氮?dú)庵袑?duì)氧化鉿進(jìn)行退火,然后進(jìn)行犧牲硅帽退火以提高其熱穩(wěn)定性,優(yōu)化了 nMOS 的有效功函數(shù)。對(duì)于鑭偶極柵疊層,6 埃 LaO 通過(guò) ALD 沉積,并用 2nm TiN 和 5nm 犧牲 a-Si 覆蓋。a-Si 的推進(jìn)退火和濕法去除在 TiAl 和 W 下留下 TiN。加蓋的柵極堆疊經(jīng)受了 4 小時(shí)的 550° 至 600°C 退火。最終有效功函數(shù)為 4.4eV,柵極泄漏減少,有效氧化層厚度為 14 埃。使用環(huán)形振蕩器和 SRAM 演示了性能。

結(jié)論

3D NAND 縮放一直是移動(dòng)設(shè)備功能的福音,芯片制造商正在繼續(xù)堆疊字線層以提高性能和位密度。最終,NAND 設(shè)備可能需要替代材料、新配置,甚至每個(gè)單元超過(guò)四位。

與此同時(shí),5G SoC 繼續(xù)為手機(jī)用戶帶來(lái)高性能和長(zhǎng)續(xù)航,似乎沒(méi)有任何直接限制。然而,這一切都不容易。晶體管和互連優(yōu)化都是擴(kuò)展到 5nm 及更高工藝的關(guān)鍵,而針對(duì)低功耗和低泄漏優(yōu)化的外圍 DRAM 電路對(duì)高熱預(yù)算工藝更為敏感。好消息是功函數(shù)調(diào)整和更換高 k 金屬柵極似乎是推動(dòng)因素。

評(píng)論