萊迪思半導體公司和Helion Technology今日宣布一系列適用于LatticeECP3 FPGA系列的壓縮和加密的IP核現已上市。該系列具有有效載荷壓縮系統核,提高了有限信道帶寬的利用率,因此非常適合微波回程應用、寬帶無線接入適用于802.16e(WiMAX)以及潛在的其他多鏈路多輸入-多輸出(MIMO)應用中的使用。在LatticeECP3器件中,IP核可以從500Mbps無縫擴展至超過3Gbps,并可用于典型的網絡應用中的第2層或第3層。IP核采用了非常強大和成熟的LZRW無損壓縮算法,它

關鍵字:

萊迪思 FPGA

萊迪思半導體公司(NASDAQ: LSCC)今天宣布,其屢獲殊榮的Platform Manager?系列產品完全合格并進入量產階段。與此量產信息發布相配合的是更新的PAC-Designer? 6.0.1設計軟件,它使模擬和電路板設計師將電路板的電源管理和數字板的管理功能集成至Platform Manager器件系列。此外,現在即可獲取另外11個參考設計(包括風扇控制器,邊界掃描端口連接器和GPIO擴展器),這些都為使用Platform Manager產品而進行了專門的測試。

關鍵字:

萊迪思 電路板

萊迪思半導體公司今天宣布推出印刷版的書“Power 2 You”, 針對電路板的電源管理功能,為設計人員提供150頁的技術細節和設計考慮。作者是Srirama(“Shyam”) Chandra,他是電源管理領域被認可的專家,發表了多篇有關電源管理的文章。

關鍵字:

萊迪思 電源管理

萊迪思半導體公司今天宣布推出其新的MachXO2? PLD系列,為低密度PLD的設計人員提供了在單個器件中前所未有的低成本,低功耗和高系統集成。嵌入式閃存技術采用了低功耗65納米工藝,與MachXO? PLD系列相比,MachXO2系列提供了3倍的邏輯密度、10倍的嵌入式存儲器、降低了100倍以上的靜態功耗并減少了高達30%的成本。

關鍵字:

萊迪思 PLD

萊迪思半導體公司今日發布了ispLEVER? Classic設計工具套件1.4版。ispLEVER Classic設計軟件已經升級,添加了帶有HDL Analyst功能集的Synopsys Synplify Pro,以及改進的ispMACH? 4000ZE CPLD Fitter,具有更好的功耗優化功能。

Synplify Pro HDL Analyst為設計師們提供了快速直觀地實現高階寄存器傳輸級(RTL)Verilog或VHDL的方法。設計師可以在圖和源代碼之間進行交叉查詢,

關鍵字:

萊迪思 設計工具套件 ispLEVER

引言

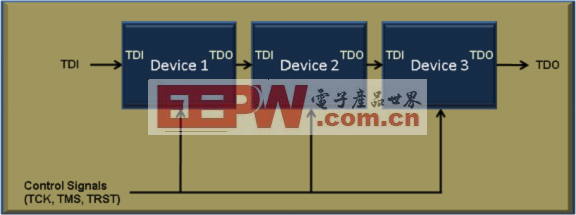

隨著JTAG標準IEEE1149.1的定型,及隨后開始在集成電路Intel 80486中采用,邊界掃描測試已被廣泛應用于測試印刷電路板的連接,以及在集成電路內進行測試。邊界掃描測試受到設計人員的歡迎,因為它能夠在線測試,而無需昂貴的釘床在線測試設備。然而,在大的電路板上,邊界掃描鏈路很長,電路板設計人員面臨著多種挑戰,諸如故障檢測和隔離、測試時間、物理布線,同時還要管理偏移,電壓轉換和滿足各種特殊需要。傳統上使用ASSP來應對這些挑戰,然而基于ASSP的解決方案更為昂貴,有固定的電平和一些

關鍵字:

萊迪思 PLD

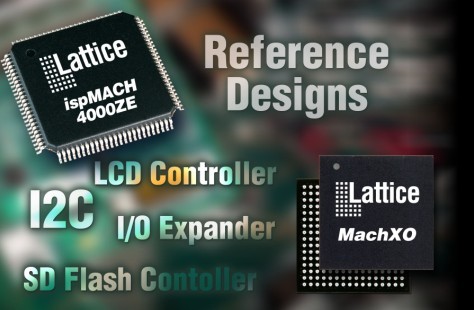

萊迪思半導體公司今天宣布已經推出了針對MachXO™和ispMACH® 4000ZE PLD而優化的超過90個參考設計。參考設計能夠幫助設計人員快速和高效地進行設計,并能有效使用這些常用功能,諸如通用I/O擴展、I2C總線主/從、LCD控制器、SD閃存控制器,以及其他接口,這些功能廣泛地用于各種市場,包括消費、通訊、計算機,工業和醫療等。這些參考設計與完整的文檔和設計源代碼結合在一起完全可以適應客戶的需求,使設計人員縮短設計時間,提高工作效率并加快產品的上市。

&ldqu

關鍵字:

萊迪思 參考設計 PLD

萊迪思半導體公司今日宣布Nu Horizons Electronics Corp. 即日起將在全球范圍內代理萊迪思的全部產品。Nu Horizons目前在整個亞太地區代理萊迪思產品。

Nu Horizons全球代理部總裁Kent Smith 表示:“Nu Horizons Electronics 非常高興能與萊迪思一起拓展全球業務。萊迪思是全球領先的FPGA、PLD、可編程時鐘和電源管理器件、軟件設計工具和IP核供應商之一,并且我們的全球銷售和工程師團隊對于可編程邏輯技術非常了解。萊

關鍵字:

萊迪思 FPGA PLD 可編程時鐘 電源管理器件

萊迪思半導體公司今日發布ispClock 5400D 可編程時鐘器件的評估板,價格為169美元。這款新的評估板是適用于ispClock5400D差分時鐘分配器件的評估和設計的易于使用的開發平臺。該款評估板還可以用于查看5400D器件的性能和在系統編程,或者用作LatticeECP3™ FPGA串行協議或視頻協議評估板的副板或時鐘源。

通常,只有帶有LVDS或LVPECL接口的價格昂貴的振蕩器才可用作FPGA SERDES接口應用的參考時鐘源。而現在ispClock5400D器件提供超

關鍵字:

萊迪思 開發平臺 LatticeECP3

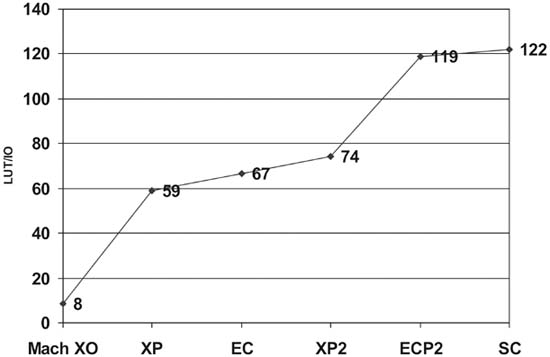

進行硬件設計的功能調試時,FPGA的再編程能力是關鍵的優點。CPLD和FPGA早期使用時,如果發現設計不能正常工作,工程師就使用“調試鉤”的方法。先將要觀察的FPGA內部信號引到引腳,然后用外部的邏輯分析儀捕獲數據。然而當設計的復雜程度增加時,這個方法就不再適合了,其中有幾個原因。第一是由于FPGA的功能增加了,而器件的引腳數目卻緩慢地增長。因此,可用邏輯對I/O的比率減小了,參見圖1。此外,設計很復雜時,通常完成設計后只有幾個空余的引腳,或者根本就沒有空余的引腳能用于調試。

關鍵字:

萊迪思 FPGA 邏輯分析儀

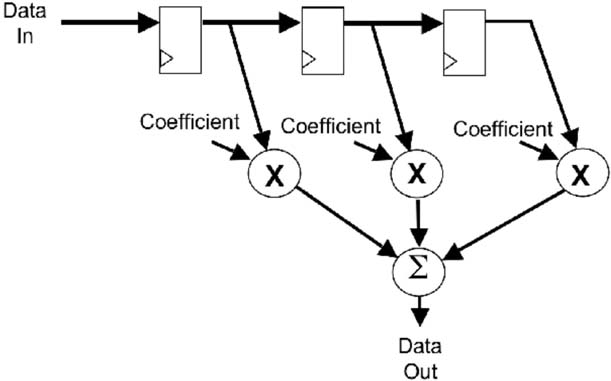

你接到要求用FPGA實現FIR濾波器的任務時,也許會想起在學校里所學的FIR基礎知識,但是下一步該做什么呢?哪些參數是重要的?做這個設計的最佳方法是什么?還有這個設計應該怎樣在FPGA中實現?現在有大量的低成本IP核和工具來幫助你進行設計,因為FIR是用FPGA實現的最普通的功能。

關鍵字:

萊迪思 FPGA FIR濾波器

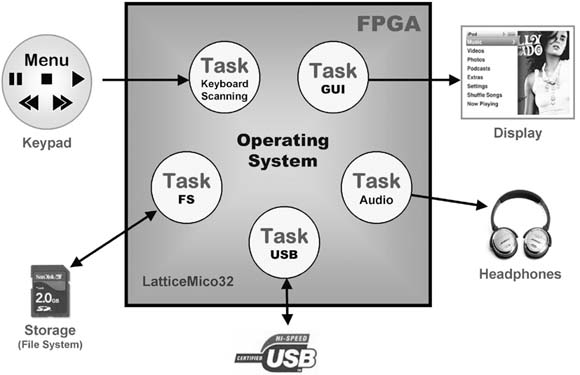

操作系統能夠提高可移植性,并提供多種經過測試的抽象層,服務層和應用模塊層以供選擇,從而加快產品上市時間并減少應用程序出錯的可能性。然而,選擇一個嵌入式操作系統( OS )從來就不是一個簡單的過程,因為集成嵌入式軟件的方式選擇余地很大,你可以完全都由自己來編寫,或通過商業定制專門實時操作系統,也可以直接購買通用操作系統不作任何修改,現成的通用操作系統。FPGA性能的提高和軟處理器核的出現,直接導致了可編程邏輯SoC解決方案的產生,隨著這一變化,關于選擇標準,設計方案以及折中考慮等傳統經驗也需要與時俱進以

關鍵字:

萊迪思 FPGA 操作系統

--第二代 EConomy Plus器件降低了50%的價格并達到雙倍的密度 -- 萊迪思半導體公司近日公布了其第二代EConomy Plus 現場可編程門陣列 (FPGA)器件,LatticeECP2系列。用了富士通90納米CMOS工藝和300毫米硅片,在大批量的情況下,此系列使得FPGA價格降到每1000查找表(LUT)低于0.50美元。與130納米 LatticeECP FPGA相比,新的系

關鍵字:

LatticeECP2 萊迪思 市場

-通力合作打造出難以超越的FPGA產品系列- 萊迪思半導體公司近日宣布推出其新一代的90納米FPGA,包含兩個全新的FPGA器件系列。LatticeSC™ 系統芯片FPGA的設計宗旨是提供業界最佳的整體性能,而LatticeECP2™ FPGA則將業界成本最低的FPGA結構和高端的FPGA功能集于一身。這兩個器件系列都采用了富士通公司經過優化的工藝,既滿足了高容量FPGA對成本效率的要求,又能夠提供擁有數百萬門的系統級FPGA所需的千兆赫性能。這兩個器件系列將在

關鍵字:

LatticeECP2 LatticeSC 富士通 萊迪思

- LatticeSC FPGA 將高速I/O、SERDES、結構化的ASIC模塊 和高性能的FPGA結構集成在單個器件上 - 萊迪思半導體公司近日發布了其LatticeSCTM系統芯片FPGA系列。該系列在高速應用中有著無以倫比的性能和連通性。LatticeSC FPGA采用富士通的90納米CMOS工藝技術并用300毫米硅片制造,能夠加速芯片至芯片、芯片至存儲器、高速串行

關鍵字:

FPGA系列 LatticeSC 萊迪思

萊迪思介紹

您好,目前還沒有人創建詞條萊迪思!

歡迎您創建該詞條,闡述對萊迪思的理解,并與今后在此搜索萊迪思的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473