用內部邏輯分析儀調試FPGA(08-100)

—— Effectively using internal logic analyzers for debugging FPGAs

推動FPGA調試技術改變的原因

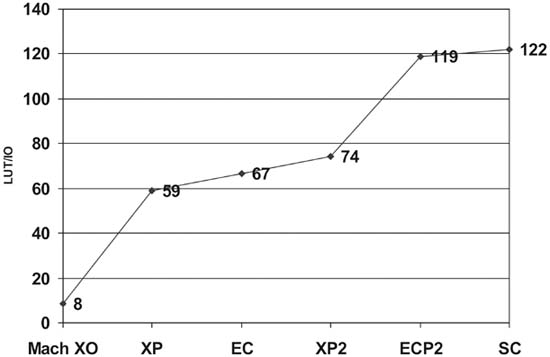

本文引用地址:http://www.104case.com/article/91697.htm進行硬件設計的功能調試時,FPGA的再編程能力是關鍵的優點。CPLD和FPGA早期使用時,如果發現設計不能正常工作,工程師就使用“調試鉤”的方法。先將要觀察的FPGA內部信號引到引腳,然后用外部的邏輯分析儀捕獲數據。然而當設計的復雜程度增加時,這個方法就不再適合了,其中有幾個原因。第一是由于FPGA的功能增加了,而器件的引腳數目卻緩慢地增長。因此,可用邏輯對I/O的比率減小了,參見圖1。此外,設計很復雜時,通常完成設計后只有幾個空余的引腳,或者根本就沒有空余的引腳能用于調試。

圖1 Lattice FPGA的LUT/可用I/O

第二,現在設計的復雜性經常需要觀察許多信號,而不是幾個信號。常用的技術是實現較寬的內部總線,以便在較大的FPGA中達到高的系統吞吐量。如果懷疑內部的32位總線里有壞的數據,則難以用幾個I/O引腳來確定問題所在。

第三,通常需要在系統中測試復雜的功能。在這種情況下,在系統中調試時訪問一些I/O也許是有限的。新類型的包還限制訪問FPGA引腳。系統速度也是個問題,因為探針的連接可能會引起性能或者噪聲信號降低。

最后,推動FPGA調試方法改變的關鍵因素是有了新的工具,這些工具采用 內部或者嵌入式邏輯分析儀。

擁有這些工具可得到最佳的結果,而不是用與先前工具相同的方法。資源、靜態參數和動態參數通常約束了內部邏輯分析儀和外部邏輯分析儀。本文對這兩種類型工具的約束進行了比較,考察如何最佳地利用內部邏輯分析儀。

評論