基于DSP高精度伺服位置環(huán)設(shè)計(jì)

當(dāng)Fpos(s)=1/(Gspd(s)Gm(s))時(shí),H(s) =1,則可使輸出完全復(fù)現(xiàn)輸入信號(hào),且系統(tǒng)的暫態(tài)和穩(wěn)態(tài)誤差都為零。其中當(dāng)速度調(diào)節(jié)器采用PI控制時(shí),在位置環(huán)的截止頻率遠(yuǎn)小于速度環(huán)的截止頻率時(shí),速度環(huán)可等效為一個(gè)慣性環(huán)節(jié),電機(jī)可等效為一個(gè)積分環(huán)節(jié),于是Fpos(s)可以看成加速度前饋和速度前饋兩部分[5],其中:位置前饋中加速度項(xiàng)差分方程:

本文引用地址:http://www.104case.com/article/95275.htm![]()

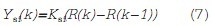

式中R(k)為第K個(gè)采樣周期中的位置給定信號(hào);Yaf為第K個(gè)采樣周期中加速度信號(hào)的輸出,Kaf為加速度前饋比例系數(shù)。

位置前饋中速度項(xiàng)差分方程:

式中R(k)為第K個(gè)采樣周期中的位置給定信號(hào);Yaf為第K個(gè)采樣周期中速度信號(hào)的輸出,Ksf為速度前饋比例系數(shù)。

相應(yīng)的位置環(huán)P的差分方程:

![]()

式中R(k)為第K個(gè)采樣周期中的位置給定信號(hào);C(k)為第K個(gè)采樣周期中的位置反饋信號(hào),Ye為第K個(gè)采樣周期中位置環(huán)信號(hào)的輸出,Kc為位置環(huán)比例系數(shù)。

絕對(duì)式編碼器通信程序

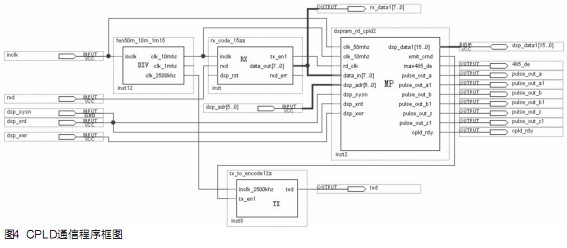

絕對(duì)式編碼器與DSP的接口采用CPLD作為接口芯片。CPLD的程序采用VHDL語(yǔ)言編寫(xiě),程序結(jié)構(gòu)如圖4所示。此電路完成串行輸入數(shù)據(jù)到并行輸出數(shù)據(jù)的轉(zhuǎn)換,以及并行輸入數(shù)據(jù)到串行輸出數(shù)據(jù)的轉(zhuǎn)換。

圖4中,模塊DIV為時(shí)鐘分頻器,TX模塊接收來(lái)自微處理器接口模塊MP的8位并行數(shù)據(jù),并通過(guò)端口DOUT將數(shù)據(jù)串行輸出到RS-485端口。反過(guò)來(lái),RX模塊接收串行數(shù)據(jù)輸入,并以8位并行格式發(fā)送至MP模塊,MP模塊同時(shí)將接收到的位置信號(hào)轉(zhuǎn)成脈沖形式輸出,實(shí)現(xiàn)與CNC的連接。

pid控制器相關(guān)文章:pid控制器原理

評(píng)論