消除狀態機毛刺策略探討

隨著EDA技術的高速發展, 以大規模和超大規模器件FPGA/CPLD為載體、以VHDL(硬件描述語言)為工具的電子系統設計越來越廣泛。有限狀態機(簡稱狀態機)作為數字系統控制單元的重要設計方案之一,無論與基于VHDL語言的其他設計方案相比,還是與可完成相似功能的CPU設計方案相比,在運行速度的高效、執行時間的確定性和高可靠性方面都顯現出強大的優勢。因此狀態機在數字電子系統設計中的地位日益凸顯。

本文引用地址:http://www.104case.com/article/82122.htm1 狀態機“毛刺”的產生

狀態機通常包含主控時序進程、主控組合進程和輔助進程三個部分。其中,主控組合進程的任務是根據外部輸入的控制信號和當前狀態的狀態值確定下一狀態的取向,并確定對外輸出內容和對內部其他組合或時序進程輸出控制信號的內容。一方面,由于有組合邏輯進程的存在,狀態機輸出信號會出現毛刺——競爭冒險現象;另一方面,如果狀態信號是多位值的,則在電路中對應了多條信號線。由于存在傳輸延遲,各信號線上的值發生改變的時間則存在先后,從而使得狀態遷移時在初始狀態和目的狀態之間出現臨時狀態——毛刺。

例如,采用Moore型有限狀態機方案對ADC0809采樣過程實現控制,其主要程序如下:

begin

lock <=lock1;

process(current_state,eoc)

begin

case current_state IS

when st0=>ale<=‘0’;start<=‘0’;oe<=‘0’;lock1<=‘0’;

next_state <=st1;

when st1=>ale<=‘1’;start<=‘0’;oe<=‘0’;lock1<=‘0’;

next_state <=st2;

when st2=>ale<=‘0’;start<=‘1’;oe<=‘0’;lock1<=‘0’;

next_state <=st3;

when st3=>ale<=‘0’;start<=‘0’;oe<=‘0’;lock1<=‘0’;

if (eoc=‘1’) then next_state <=st3;

else next_state <=st4;

end if;

when st4=> ale <=‘0’;start <=‘0’;OE<=‘0’;lock1<=‘0’;

if (eoc =‘0’) then next_state <=st4;

else next_state <=st5;

end if;

when st5=> ale <=‘0’; start <=‘0’;oe<=‘1’;lock1<=‘0’;

next_state <=st6;

when st6=> ale <=‘0’; start <=‘0’; oe <=‘1’;lock1<=‘1’;

next_state <=st0;

when others=> ale <=‘0’; start <=‘0’;oe <=‘0’;lock1<=‘0’;

next_state <=st0;

end case;

end process;

process (clk)

begin

if (clk’event and clk =‘1”) then

current_state <=next_state;

end if;

end process;

process(lock1)

begin

if lock1=‘1’ and lock1’event then

regl<=d;

end if;

end process;

q<=regl;

……

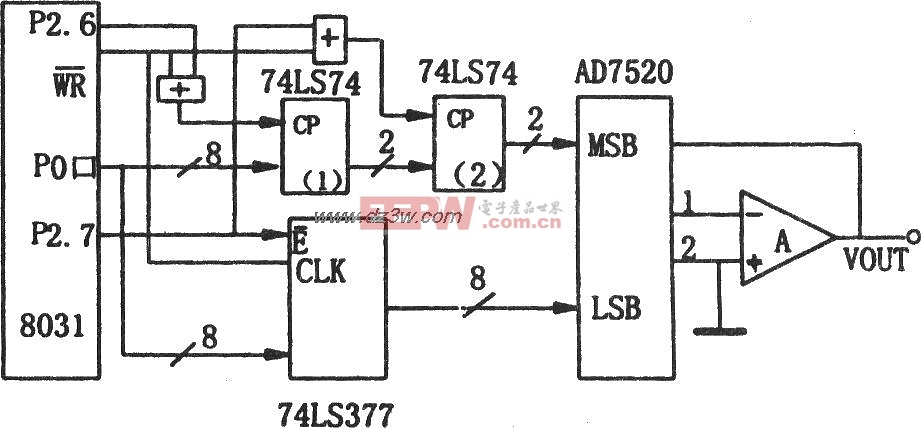

其時序仿真波形如圖1所示。

Moore型狀態機組成框圖如圖2所示。

因為Moore型狀態機的輸出信號來自組合邏輯——輸出譯碼器,輸出信號中帶有“毛刺”,且引起了輸出信號Q的誤動作,結果從其仿真時序圖中可以發現。

2 毛刺的消除

在同步電路中,一般情況下“毛刺”不會產生重大影響。因為“毛刺”僅發生在時鐘有效邊沿之后的一小段時間內,只要在下一個時鐘有效邊沿到來之前“毛刺” 消失即可。但當狀態機的輸出信號作為其他功能模塊的控制信號,例如作為異步控制、三態使能控制或時鐘信號使用時,將會使受控模塊發生誤動作,造成系統工作混亂。因此,在這種情況下必須通過改變設計消除毛刺。

消除狀態機輸出信號的“毛刺”一般可采用三種方案:

(1)調整狀態編碼,使相鄰狀態間只有1位信號改變,從而消除競爭冒險的發生條件,避免了毛刺的產生。常采用的編碼方式為格雷碼。它適用于順序遷移的狀態機。

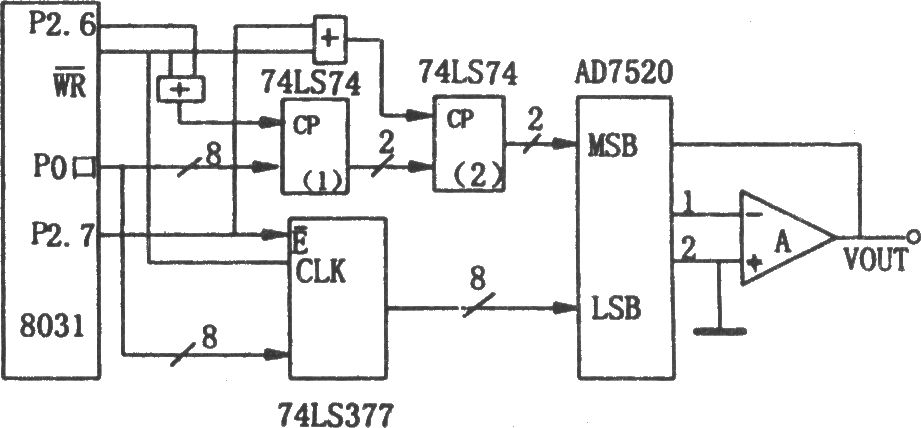

(2)在有限狀態機的基礎上采用時鐘同步信號,即把時鐘信號引入組合進程。狀態機每一個輸出信號都經過附加的輸出寄存器,并由時鐘信號同步,因而保證了輸出信號沒有毛刺,如圖3所示。這種方法存在一些弊端:由于增加了輸出寄存器,硬件開銷增大,這對于一些寄存器資源較少的目標芯片是不利的;從狀態機的狀態位到達輸出需要經過兩級組合邏輯,這就限制了系統時鐘的最高工作頻率;由于時鐘信號將輸出加載到附加的寄存器上,所以在輸出端得到信號值的時間要比狀態的變化延時一個時鐘周期。

(3)直接把狀態機的狀態碼作為輸出信號,即采用狀態碼直接輸出型狀態機,使狀態和輸出信號一致,使得輸出譯碼電路被優化掉了,因此不會出現競爭冒險。這種方案,占用芯片資源少,信號與狀態變化同步,因此速度快,是一種較優方案。但在設計過程中對狀態編碼時可能增加狀態向量,出現多余狀態。雖然可用CASE語句中WHENOTHERS來安排多余狀態,但有時難以有效控制多余狀態,運行時可能會出現難以預料的情況。因此它適用于狀態機輸出信號較少的場合。

若對ADC0809的采樣控制采用狀態碼直接輸出型狀態機方案,其主要程序如下:

begin

lock<=lock1;

process(current_state,eoc)

begin

case current_state IS

when st0 => next_state <=st1;

when st1 => next_state <=st2;

when st2 => next_state <=st3;

when st3 => if (eoc =‘1’)then next_state <=st3; else next_state <=st4;end if;

when st4 => if (eoc =’0’)then next_state<=st4;else next_state <=st5; end if;

when st5 => next_state <=st6;

when st6 => next_state <=st0;

when others=> next_state <=st0;

end case;

out4<=current_state(5 downto 2);

ale<=current_state(5); start <=current_state(4);

oe<=current_state(3); lock1<=current_state(2);

end process;

process(clk)

begin

if (clk’event and clk =‘1’) then

current_state <=next_state;

end if ;

end process ;

process (lock1)

if lock1=‘1’ and lock1’event then

regl<=d ;

end if ;

end process ;

q<=regl;

……

電子血壓計相關文章:電子血壓計原理

評論