- 組合邏輯設計中的毛刺現象-和所有的數字電路一樣,毛刺也是FPGA電路中的棘手問題,它的出現會影響電路工作的穩定性,可靠性,嚴重時會導致整個數字系統的誤動作和邏輯紊亂。

- 關鍵字:

毛刺 FPGA 電路

- 只要輸入信號同時變化,(經過內部走線)組合邏輯必將產生毛刺。將它們的輸出直接連接到時鐘輸入端、清零或置位端口的設計方法是錯誤的,這可能會導致嚴重的后果。 所以我們必須檢查設計中所有時鐘、清零和置位等對毛刺敏感的輸入端口,確保輸入不會含有任何毛刺。

- 關鍵字:

毛刺 置位信號 FPGA

- 毛刺問題在FPGA設計中非常關鍵,只有深刻理解毛刺的本質,才有可能真正掌握設計的精髓,本文就FPGA設計中的毛刺問題進行了深入的探討,分析其產生的原因和條件,給出了幾種常用的消除方法,希望對FPGA設計者有一定的參考作用。

- 關鍵字:

毛刺 同步脈沖 FPGA

- 該篇將分析對象限定為一個DAC,其中的輸出緩沖器在正常模式下被加電:零量程或中量程。文章將分析一下DAC輸出在高阻抗模式中被加電的情況。

- 關鍵字:

DAC 毛刺

- 摘要 針對基于單片機的IRIG—B碼解碼器解碼精度低、工作穩定性差等問題,提出了一種基于FPGA的IRIG—B碼解碼器設計。在實現過程中著重分析了輸

- 關鍵字:

IRIG―B碼 解碼 毛刺

- 狀態機“毛刺”的產生及消除措施,隨著EDA技術的高速發展, 以大規模和超大規模器件FPGA/CPLD為載體、以VHDL(硬件描述語言)為工具的電子系統設計越來越廣泛。有限狀態機(簡稱狀態機)作為數字系統控制單元的重要設計方案之一,無論與基于VHDL語言的其他

- 關鍵字:

措施 消除 產生 毛刺 狀態

- 使用EP2C35 FPGA 設計了多個串口工作,出現了幾個問題. 第一次, 由于內核電源1.2V 供電不是完整平面,而是帶狀線供電,EP2C35 在代碼容量大的情況下,而且輸入FPGA 信號變換頻繁, 造成整個EP2C35 所有的D觸發器停止翻轉.

- 關鍵字:

FPGA 線路 尖峰 毛刺

- 狀態機“毛刺”的產生及消除方法程序, 隨著EDA技術的高速發展, 以大規模和超大規模器件FPGA/CPLD為載體、以VHDL(硬件描述語言)為工具的電子系統設計越來越廣泛。有限狀態機(簡稱狀態機)作為數字系統控制單元的重要設計方案之一,無論與基于VHDL語言的其

- 關鍵字:

方法 程序 消除 產生 毛刺 狀態

- 數字射頻(RF)技術迅速發展帶來一個結果,就是頻譜越來越擁擠,使用效率也越來越高;與此同時,現代RF信號也變得異常復雜。為了改善容量、性能及保密性,一般會結合使用完善的RF技術,如突發、跳頻和自適應調制,這些

- 關鍵字:

頻譜分析儀 毛刺 RF信號 瞬態

- FPGA設計中毛刺信號解析,在FPGA的設計中,毛刺現象是長期困擾電子設計工程師的設計問題之一, 是影響工程師設計效率和數字系統設計有效性和可靠性的主要因素。由于信號在FPGA的內部走線和通過邏輯單元時造成的延遲,在多路信號變化的瞬間,組合

- 關鍵字:

解析 信號 毛刺 設計 FPGA

- 0 引言 電壓毛刺是高頻變換器研制和生產過程中的棘手問題,處理得不好會帶來許多的問題,諸如:功率管的耐壓必須提高,而且耐壓越高,其通態電壓越大,功耗越大,這不僅使產品效率降低,而且使電路可靠性降低

- 關鍵字:

電路 無損 吸收 毛刺 新型 整流 高頻 電壓

- 狀態機“毛刺”的產生及消除方法, 隨著EDA技術的高速發展, 以大規模和超大規模器件FPGA/CPLD為載體、以VHDL(硬件描述語言)為工具的電子系統設計越來越廣泛。有限狀態機(簡稱狀態機)作為數字系統控制單元的重要設計方案之一,無論與基于VHDL語言的其

- 關鍵字:

方法 消除 產生 毛刺 狀態

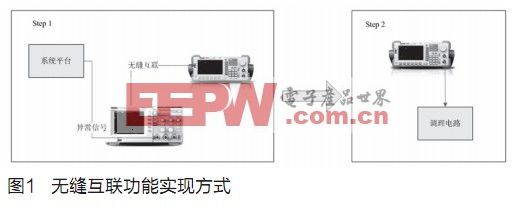

- 在實際的電路運行中,由于各種干擾和響應的存在,實際電路往往存在各種缺陷信號和瞬變信號,如果在設計之初沒有考慮這些情況,往往會產生災難性的后果。找到這些異常信號,根據這些信號的特性選擇合適的調理電路加以抑制和優化,這一直是電子工程師們所頭疼的。本文以普源精電DS1302CA示波器及其新近推出的DG5000系列函數/任意波形發生器為例來介紹無縫互聯功能的實現方式。

- 關鍵字:

任意波形發生器 示波器 毛刺 無縫互聯 201008

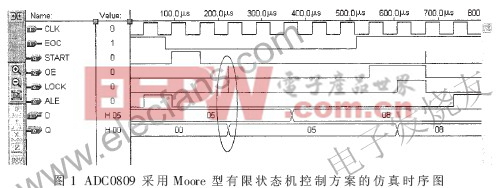

- 隨著EDA技術的高速發展, 以大規模和超大規模器件FPGA/CPLD為載體、以VHDL(硬件描述語言)為工具的電子系統設計越來越廣泛。有限狀態機(簡稱狀態機)作為數字系統控制單元的重要設計方案之一,無論與基于VHDL語言的其他設計方案相比,還是與可完成相似功能的CPU設計方案相比,在運行速度的高效、執行時間的確定性和高可靠性方面都顯現出強大的優勢。因此狀態機在數字電子系統設計中的地位日益凸顯。

1 狀態機“毛刺”的產生

狀態機通常包含主控時序進程、主控組合進程和輔助

- 關鍵字:

EDA 有限狀態機 毛刺

毛刺介紹

您好,目前還沒有人創建詞條毛刺!

歡迎您創建該詞條,闡述對毛刺的理解,并與今后在此搜索毛刺的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473