嵌入式邏輯分析儀在FPGA時序匹配設計中的應用(07-100)

——

使用Signal Tap II時應注意:

本文引用地址:http://www.104case.com/article/81757.htm·用Signal Tap II 采集數據時,應符合采樣定律,即采樣頻率必須是信號最大頻率的兩倍或更高,否則采集到的波形會失真或者是一條全低的直線。

·采樣深度決定了每個信號可存儲的采樣數目,信號的數量和采樣深度的乘積不能超過所選FPGA芯片內部RAM的大小,添加待觀察信號、設置了采樣深度后,可以根據Signal Tap II的Instance Manager 窗口觀察內部存儲資源的使用情況。如果觀察的信號數量多,采樣深度設置受到限制,此時靈活設置觸發條件相當必要。圖4和圖7采集的波形都是以設置RGBdin[23..16]為00h為觸發條件,如圖4,7中的虛線所示。

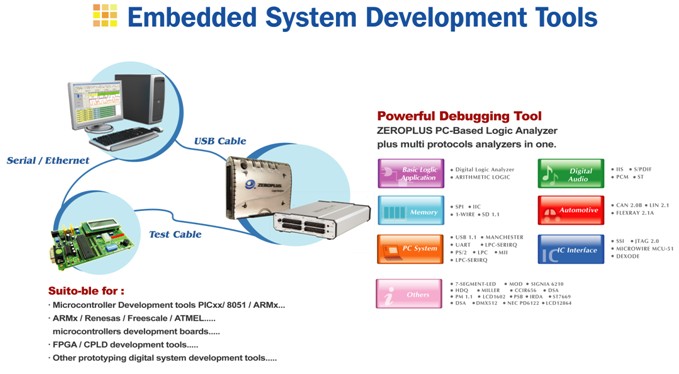

·Signal Tap II必須工作在JTAG方式,調試完成后應將Signal Tap II文件移除,以免浪費FPGA資源。

結語

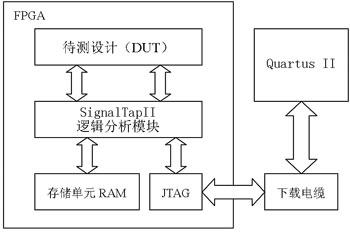

時序匹配是FPGA電路設計中的一個重要問題,介紹了一種應用嵌入式邏輯分析儀Signal Tap II捕獲FPGA內部信號波形的方法,通過比較分析采集的數據,可得出精確的延時信息,指導FPGA時序匹配的設計。

以LED全彩大屏同步顯示控制系統中顯示驅動控制部分的位面分離模塊為例,在嵌入式邏輯分析儀Signal Tap II的時序測試結果的指導下,設計一個由34個D觸發器構成的時序匹配模塊,經實際電路的波形測試證明,信號時序匹配良好。

評論