嵌入式邏輯分析儀在FPGA時序匹配設計中的應用(07-100)

引言

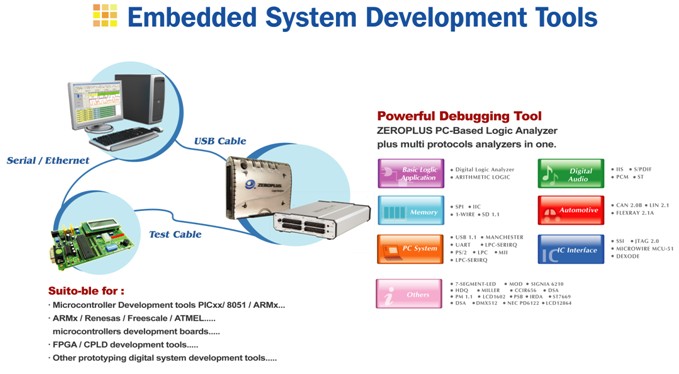

本文引用地址:http://www.104case.com/article/81757.htm隨著FPGA器件規模的不斷增加、封裝密度不斷提高,傳統邏輯分析儀在FPGA板級調試中的應用日益困難。為此,主流FPGA廠商相繼在其開發工具中增加了嵌入式邏輯分析儀(ELA) IP軟核,如Lattice在ispLEVER中提供的ispTRACY,Xilinx在ISE中提供的ChipScopePro,Altera在Quartus II提供中的Signal Tap II等。ELA在FPGA內部預先設計探測點和測試邏輯,可在軟件工具的配合下對FPGA設計進行較全面的測試。采用ELA,只需用JTAG下載電纜連接待調試的FPGA器件,占用FPGA的部分邏輯資源和內部存儲器資源,無需傳統的邏輯分析儀就可以觀察FPGA的內部信號和I/O引腳的狀態。

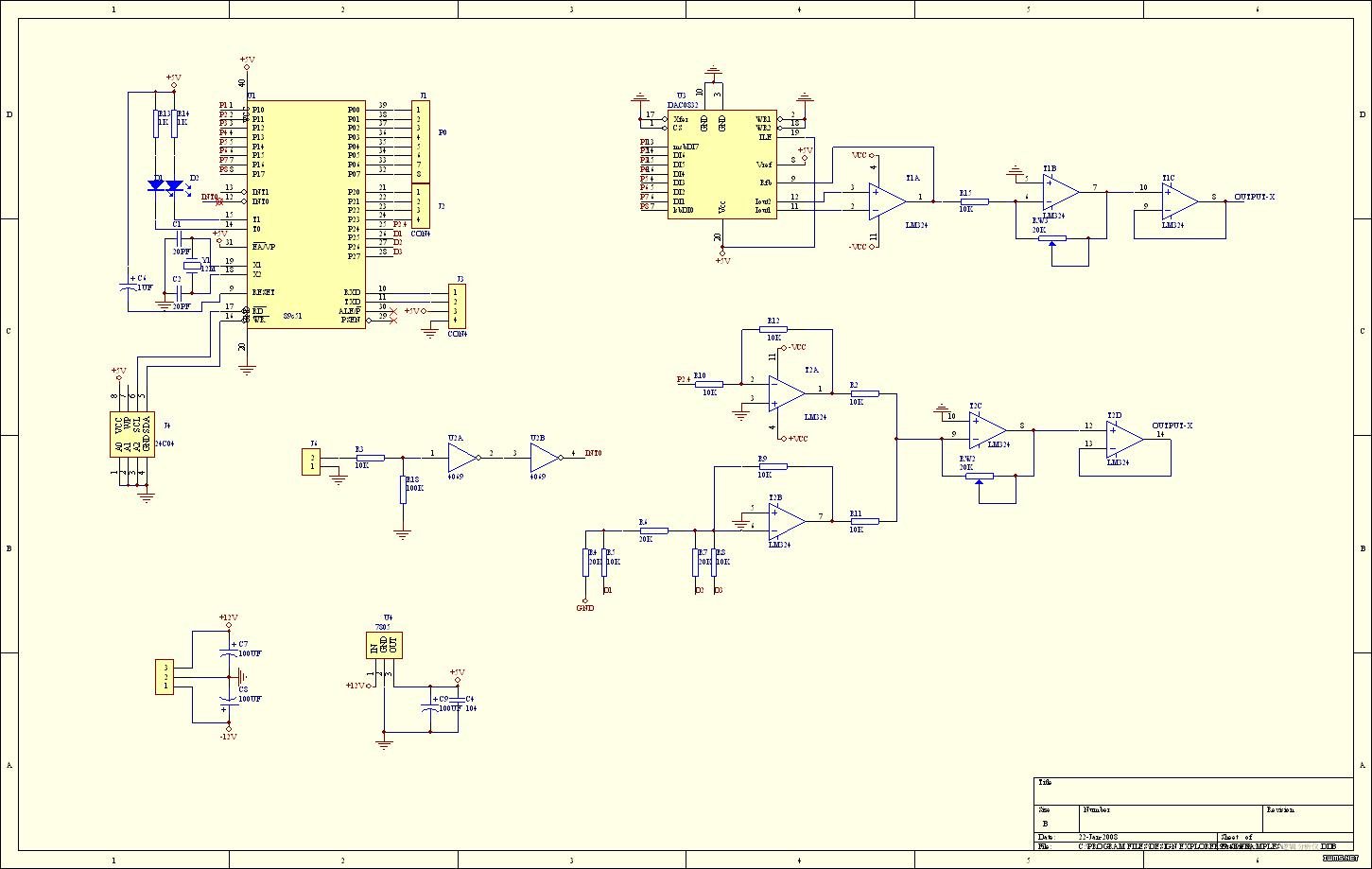

以我們開發的全彩LED同步顯示控制系統為例,該系統包括采集、傳輸、接收等模塊,FPGA為Altera Cyclone系列PQFP封裝的EP1C6Q240C8,邏輯單元(LE)數量為5980個,RAM大小為92160 bit。使用Quartus II軟件首次對設計文件進行綜合布局和布線,將布線好的工程下載到FPGA板上運行時,全彩LED屏顯示效果非常差,圖像閃爍且左右移動。根據Quartus II編譯報告可以看出,該工程消耗的器件資源僅為26%,但是卻占用了90%的引腳,留給外部測試的引腳僅為10%,使得利用Quartus II內部集成軟件測試的優勢得以體現。為了找出設計缺陷,采用Signal Tap II采集到FPGA內各個關鍵信號的波形,根據波形找出原因在于LED顯示屏接收板中的數據信號較控制信號形成了延時,造成了時序不匹配。

本文介紹的FPGA時序匹配設計方法,利用Quartus II軟件中的Signal Tap II采集FPGA內部信號波形,通過比較分析采集的數據,可得出精確的延時信息。在Signal Tap II時序測試結果的指導下改進了設計,經實際電路的波形測試證明,LED顯示屏接收板中的數據信號與控制信號時序匹配良好。

Signal Tap II

Signal Tap II是Altera公司FPGA開發軟件Quartus II中的一個實用工具,能夠捕獲、顯示FPGA內部節點或I/O引腳實時信號的狀態,幫助設計者在系統設計時觀察硬件和軟件的交互作用。

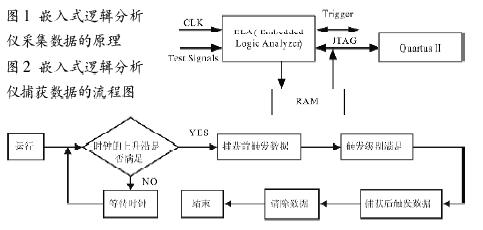

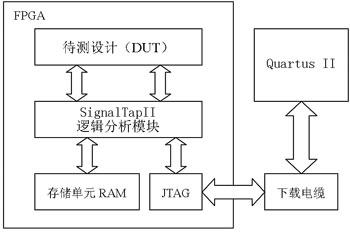

圖1為Signal Tap II嵌入式邏輯分析儀采集數據的原理框圖。其中CLK(采樣時鐘)和Trigger(觸發邏輯)可以根據需要設定。在Signal Tap II工作時,待測試信號在CLK的上升沿被嵌入式邏輯分析儀實時捕獲,經FPGA內部的RAM緩存后,通過JTAG接口傳送至Quratus II軟件中顯示。其中,RAM緩存方式有連續存儲和分段存儲。JTAG接口用的下載電纜包括USB Blaster、ByteBlasterMV、ByteBlaster II或MasterBlaster等。這些在Signal Tap II工作窗口可以靈活設置。

嵌入式邏輯分析儀捕獲數據的流程如圖2所示。首先判斷時鐘的上升沿是否滿足,不滿足繼續等待時鐘,滿足先捕獲前觸發數據,觸發級別滿足后,捕獲后觸發數據,然后清除數據,結束該捕獲流程。其中Signal Tap II最多可支持10級觸發級別。觸發級別高意味著可接收更復雜的數據獲取命令,提供更高的精度和問題解決能力。

使用Signal Tap II設計時序匹配電路

延時的產生

在LED全彩大屏同步顯示控制系統中,針對占空比控制亮度損失大的問題,在顯示驅動控制模塊設計中采用了分場疊加與占空比控制相結合的方法對存儲的圖像數據進行分場掃描,實現了低亮度損失、800×512分辨率、256級灰度LED全彩大屏的顯示。其中,“分場疊加”是指:前端將一幅彩色圖像的數據按灰度級分解為多個位平面,終端根據不同位平面數據掃描不同的場次,在有限時間內實現各場次的疊加,從而在LED全彩大屏上重建彩色圖像。

評論