嵌入式邏輯分析儀在FPGA時序匹配設計中的應用(07-100)

根據理論計算,一個D觸發器會帶來一個clk156的時鐘的延時,那么要延時9個clk38的時鐘必須使用36個D觸發器。實際上,D觸發器固定的建立時間、保持時間,也會帶來系統延時。根據Signal Tap II采集的波形對D觸發器的個數進行適當的刪減,達到了精確的9個clk38時鐘的延時,最后的時序匹配模塊由34個D觸發器構成。

本文引用地址:http://www.104case.com/article/81757.htm 圖6為時序匹配模塊的內部框圖。D觸發器D端口接flag,clk端口接clk156,第30個和第34個D觸發器Q端口分別連接Flag_delay8和flag_delay9。該時序匹配模塊采用四倍于clk38的clk156作為驅動時鐘,以確保延時信號的相位延時足夠精確。

圖7為Signal Tap II采集時序匹配模塊的波形輸出。其采樣時鐘為38MHz,采樣深度為4K bit。rgb_regroup_output[23..0]為位面分離后紅色輸出的數據。可以看出,輸出數據在flag_delay9的上升沿開始由FFh(高阻)變成有效數據00h,達到了數據和控制信號的完全同步。

性能分析

把該時序匹配模塊加入工程,重新綜合布局布線,下載到全彩LED大屏同步顯示控制系統的接收板上,Quartus II編譯報告中除了占用部分內部存儲器資源和LE資源,其它的(如I/O引腳的利用率)都沒有變化。觀察LED大屏顯示效果,圖像清晰穩定,證明了該時序匹配模塊的可行性。

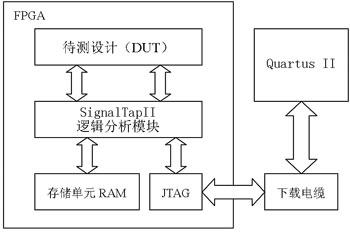

該時序匹配模塊僅為LED同步顯示控制系統中一個最簡單的模塊,用于示例說明嵌入式邏輯分析儀Signal Tap II在FPGA時序匹配設計中的應用方法。應用Signal Tap II還能解決各種各樣的問題,如外部存儲器的雙向數據口的實時波形檢測、驅動模塊的并串轉換波形等。使用Signal Tap II有如下優點:

·不占用額外的I/O引腳。利用Signal Tap II成功的采集了FPGA內部信號的波形,如flag,flag_delay8,flag_delay9等都為FPGA內部寄存器信號。

·Signal Tap II為硬件板級調試工具,它采集的波形是工程下載后的實時波形,方便設計者查找引起設計缺陷的原因。

·節約成本。Signal Tap II集成在Quartus II軟件中,無需另外付費。

評論