嵌入式邏輯分析儀在FPGA時序匹配設計中的應用(07-100)

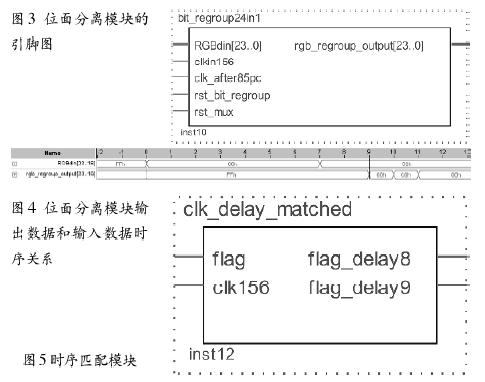

圖3為位面分離模塊在Quartus II軟件中生成的引腳圖。其中RGBdin[23..0]為輸入的顏色數據(R、G、B三種顏色各八位),clkin156為輸入數據時鐘,clk_after85pc為延時后的使能信號,rst_bit_regroup為移位寄存器的復位信號,rst_mux為顏色位選擇器的復位信號,rgb_regroup_output[23..0]是經過數據重組后輸出的數據。

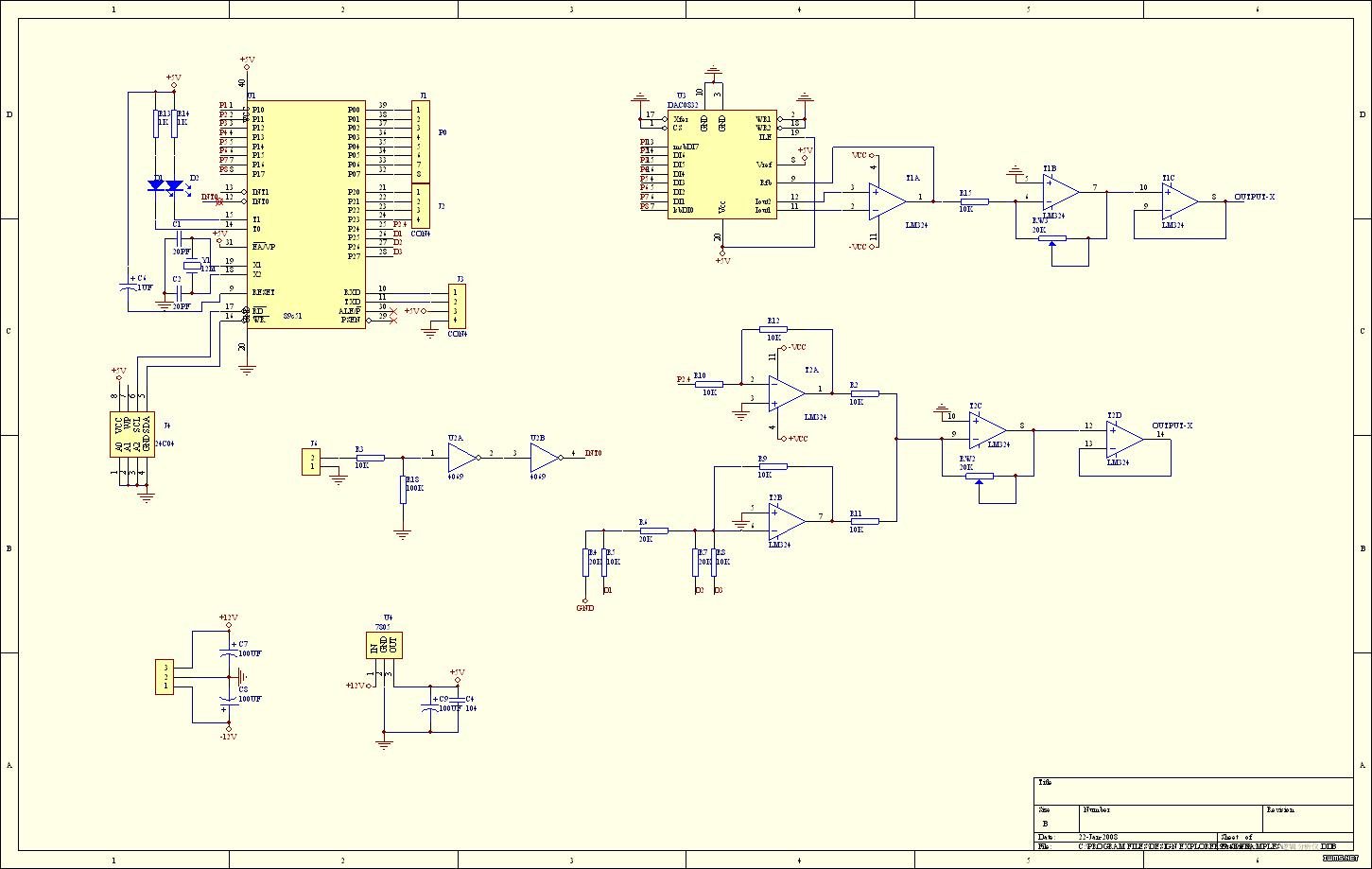

“位面分離模塊”實現“分場存儲”功能,即將每個顏色的8比特數據(以256級灰度為例)按灰度級分類,分別存入存儲器的8個數據段中。位平面的分離需要時間,將帶來系統延時。圖4為利用Signal Tap II采集的輸入數據RGBdin[23..16]和輸出數據rgb_regroup_output[23..16]的波形關系。其中采樣時鐘設置為clk38 (CRT顯示器分辨率為800×600,刷新頻率為60Hz,輸出的點時鐘為38MHz),采樣深度設置為4K bit,則Signal Tap II采集波形時占用了16×4K=64K bit個存儲單元。

由圖4 (黑色亮線)可以看出,輸出數據在第9個時鐘(clk38)時由FF(高阻)變成有效數據。該模塊的輸出數據是送到外部存儲器中進行緩存的,存儲器的寫使能信號為輸入數據的數據有效信號。由于該數據延時了9個clk38時鐘,存儲器的寫使能控制信號也應延時9個clk38時鐘生效。

時序匹配設計及測試波形

基于D觸發器的延時功能,設計了如圖5所示的時序匹配模塊,解決了上述位面分離操作與寫存儲器控制信號的時序匹配問題。圖5中,flag為數據的有效信號標志,高電平時數據輸出有效;Clk156為點時鐘38MHz的四倍頻時鐘,Flag_delay8和flag_delay9分別是flag延時8個clk38時鐘和9個clk38時鐘的新的數據有效信號標志。

評論