利用SmartCompile和賽靈思的設計工具進行設計保存(07-100)

在FPGA環境下,設計保存實施比較復雜,需要保存的事項包括:一項設計的HDL描述、一個模塊的綜合網表、約束文件內的布局信息,以及在局部比特文件中的配置數據。賽靈思集成軟件環境ISE 9.1i 軟件以新的SmartCompile 技術為特色,其中包含兩種新的方法:SmartGuide和Partitions,這兩種方法可以保存像布局或布線這樣的設計執行數據,并且可以減少解決問題所花費的時間。

本文引用地址:http://www.104case.com/article/81756.htmSmartGuide采用命名和拓樸匹配技術來識別一個FPGA設計中相對于以前的實現還沒有發生改變的各個部分。在新的和已修改過的設計被重新實現時,設計中匹配元器件得到了保存。

Partitions 采用的技術中,FPGA 設計的模塊實例被自動分析,接著,與以前的模塊實現比較,確定該模塊實例是最新的還是過時的。如果Partition 是過時的,它也完全可以重新實現且不發生保存。如果Partition是最新的,它可從以前的實現中被嚴格地復制且(從綜合網表通過布線)完整地保存布局和布線運行時間。

SmartGuide如何運作?

SmartGuide工作在像查找表(LUT)和觸發器這樣的FPGA中最低級的物理單元上。這些單元及其連通性被依次匹配和保存。

要成功引導的第一步是對已經作出較小變更的設計綜合一個一致的網表。例如,減法器等式regAB=(A"B),可以被綜合成Msub_sub0001的邏輯名稱。下一個減數就稱為Msub_sub0002,并且依此類推。在引入新減數的設計中的任何變更都可能造成設計中所有減數的重新命名。為了解決這個問題,像Synplicity 公司的Synplify和Synplify Pro以及賽靈思公司的XST這樣的綜合工具,已經改變了邏輯命名的慣例。利用這些工具,無論用戶有沒有對RTL進行變更或進行了小的變更,邏輯命名從一個綜合運行到下一個綜合都變得更加可以預測。按照以上的實例, 減法邏輯就被命名為Msub_regAB_sub0001。通過采用在邏輯中的寄存器名,就能防止改變到其它的減數。

綜合命名慣例的另一項增強措施是以本地而不是全局上下文為基礎。在RTL出現小的變化以及設計沿著非關鍵路徑重新綜合時,這可能有所幫助。在綜合之后,與非關鍵時序路徑相關的邏輯被修改,而機器給未改變邏輯產生的實例名稱保持不變。綜合網表變化被本地化到網表內的已修改的或新的邏輯。最優化一向是可復制的,這是因為它們以本地邏輯為基礎。例如,作為最優化過程的一個部分,Synplicity的 Synplify/Pro目前創建路徑組(path groups),它是被分別最優化的各個邏輯組。當邏輯在非關鍵時序路徑上優化時,只有受影響的路徑組被改變,以最小化對綜合網表的影響。

在生成綜合網表后,ISE 9.1i中的實現工具會處理網表,并把它轉換成針對特定FPGA 架構的經布局和布線的設計。在匹配過程中會發生引導,所有的元器件以匹配元器件名稱為基礎被引導。如果一個元器件在目前的實現和引導設計中都有相同的名稱,那么,該元器件就能被成功地引導。該元器件可能有不同的LUT方程式或引在生成綜合網表后,ISE 9.1i中的實現工具會處理網表,并把它轉換成針對特定FPGA 架構的經布局和布線的設計。在匹配過程中會發生引導,所有的元器件以匹配元器件名稱為基礎被引導。如果一個元器件在目前的實現和引導設計中都有相同的名稱,那么,該元器件就能被成功地引導。該元器件可能有不同的LUT方程式或引腳,并仍可以成功地被引導。

如果在當前實現和引導設計中的源和負載引腳是相同的,就能對網絡進行引導。這消除了對兩次實現之間的網絡名稱要保持一致的依賴。它也極大地增加了成功引導網絡的機率。

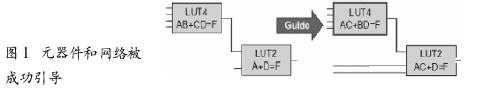

如圖1所示,例如,LUT4的邏輯等式已經被修改。LUT4將被引導,因為即使它的邏輯等式是不同的,它的相關名稱也沒有被改變。LUT4和LUT2 之間的布線將被引導,這是因為LUT4 和 LUT2之間的連通性沒有被修改。

評論