FPGA到高速DRAM的接口設計(04-100)

——

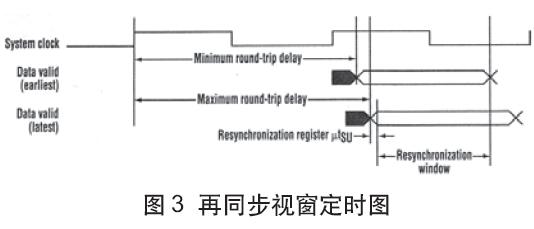

為了得到安全的再同步視窗,設計人員需要計算加上上面所列的所有延遲(稱之為往返延遲)系統的最小和最大延遲(見圖3)。用下面的方程式可得到再同步視窗:

本文引用地址:http://www.104case.com/article/80852.htm

再同步視窗=最小往返延遲+1個時鐘周期—最大往返延遲—再同步寄存器的最大微建立和/保持時間

若再同步視窗落在系統時鐘沿的外面,設計人員需要用另外的相移PLL輸出時鐘,這沿將會在此視窗內。計算往返延遲和評估再同步時鐘的時鐘相位易于出錯并且耗時。

很多時間,設計人員用不斷試驗來找出再同步時鐘相位。某些FPGA供應商提供設計幫助,可以減少或消除不斷試驗的過程。例如,Altera的再存儲器一控制器IP核具有往返延遲計算器,這可使設計人員計算他們專用系統的再同步視窗。設計人員可以輸入跡線延遲和其他專門適于他們系統的其他延遲元件。往返延遲計算器將判斷系統時鐘和DQS域之間的編移。若需要來自PLL的相移輸出,它也可以確定正確捕獲數據所需的相移量。

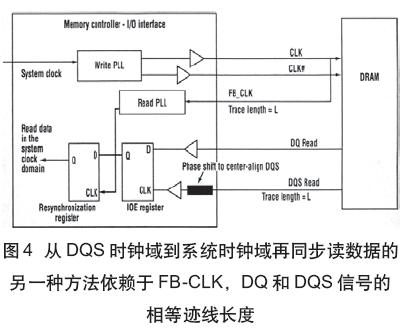

再同步的另一技術是用反饋時鐘,另外的Read PLL示于圖4。來自存儲器的反饋時鐘FB-CLK的板跡線應該與DQ和DQS信號的板跡線長度相同。FB-CLK連接到DRAM CLK引腳并返回到FPGA。Read PLL相移輸入時鐘FB-CLK,所以,它能從DQS域到系統時鐘域正確地捕獲讀數據。相移量是來自DRAM的±TDQSCK,DQS、CLK和FB-CLK跡線之間的任意板跡線偏移和IOE寄存器和再同步寄存器之間的延遲之和。

評論